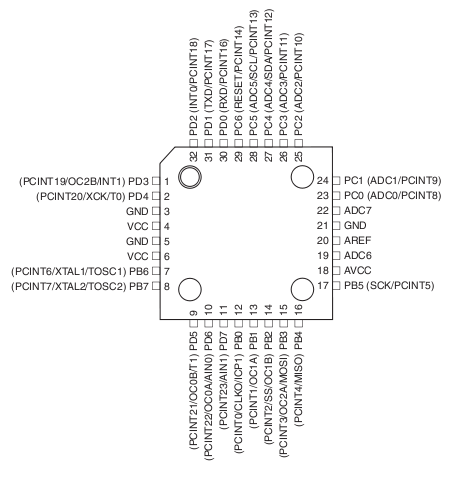

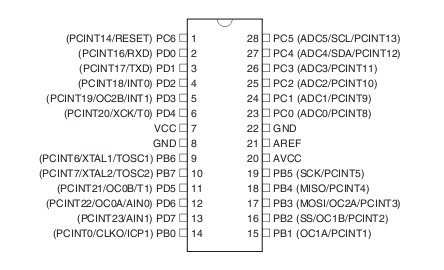

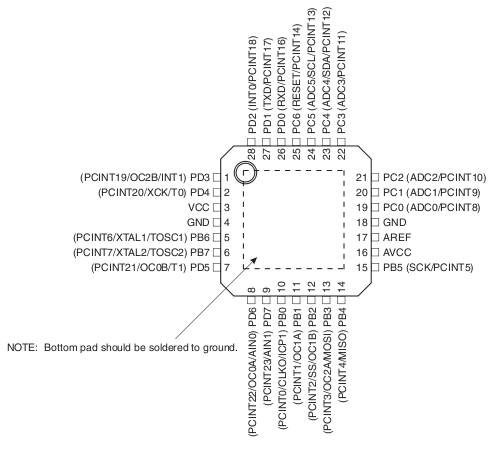

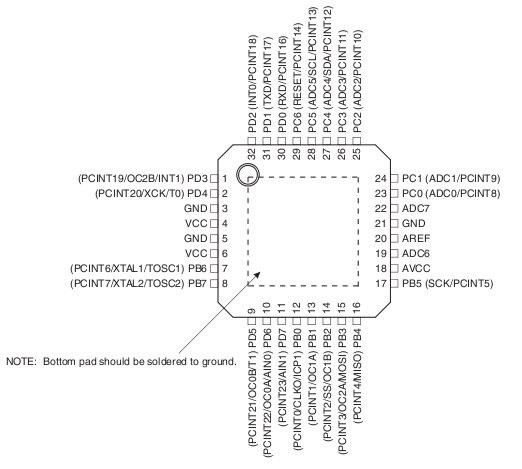

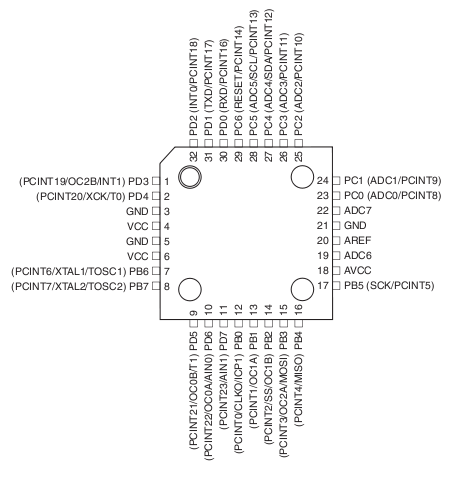

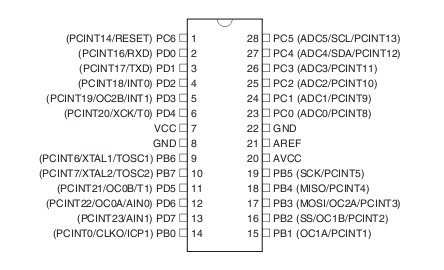

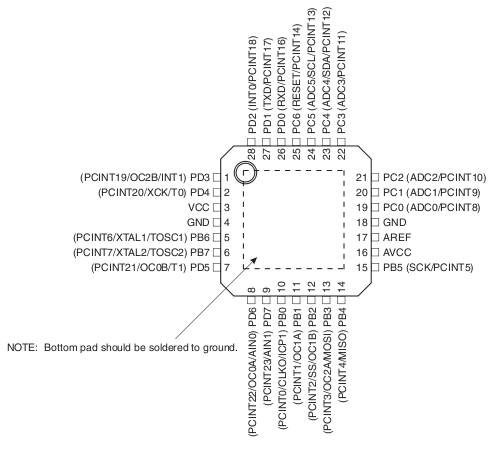

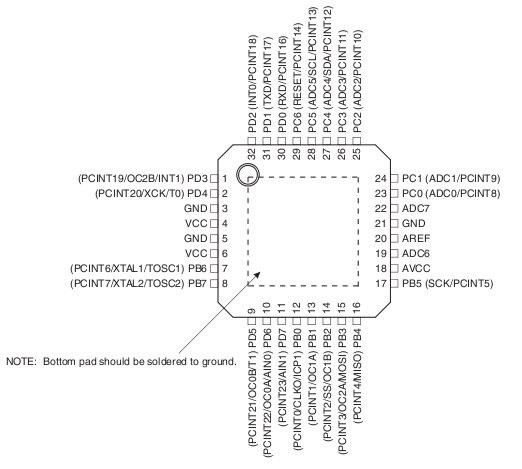

Figure 1-1. ピン接続図 ATmega48/88/168

Figure 1-1. ピン接続図 ATmega48/88/168

デジタル回路電源供給端子

グラウンド端子

ポートBは、内部にプルアップ抵抗(ビットごとに選択可能)を備えた8ビットの双方向入出力ポートです。ポートBの出力バッファは大きなシンク電流とソース電流を流すことができる対称的ドライブ能力をもっています。入力として使用するとき、外部でLowにプルダウンされている端子がプルアップ抵抗を有効にしていると、端子からソース電流が流れます。ポートBは、CPUクロックがない場合であってもリセット状態では、ハイ・インピーダンス状態になります。

クロック選択ヒューズビットの設定により、PB6はCPUクロック発振器の反転増幅回路の入力として、または、内部クロック発生回路への入力として使用することができます。

クロック選択ヒューズビットの設定により、PB7はCPUクロック発振器の反転増幅回路からの出力として使用することができます。

キャリブレート済み内部RC発振器がCPUのクロック源として使用されているとき、PB7..6は、ASSRレジスタのAS2ビットがセットされていれば、非同期タイマー/カウンター2のTOSC2..1入力として使用されます。

ポートBの様々な特殊機能については、「ポートBの機能切り替え」(p.77)、および「システム・クロックとオプション」(p.26)に詳細が記載されています。

ポートCは、内部にプルアップ抵抗(ビットごとに選択可能)を備えた7ビットの双方向入出力ポートです。PC5..0の出力バッファは大きなシンク電流とソース電流を流すことができる対称的ドライブ能力をもっています。入力として使用するとき、外部でLowにプルダウンされている端子がプルアップ抵抗を有効にしていると、端子からソース電流が流れます。ポートCは、CPUクロックがない場合であってもリセット状態では、ハイ・インピーダンス状態になります。

ポートCの様々な特殊機能については、「ポートCの機能切り替え」(p.80)に詳細が記載されています。

RSTDISBLヒューズビットが設定されていると、PC6は入出力端子として使用されます。PC6端子の電気的特性は他のポートCの端子と異なっていることに注意してください。

RSTDISBLヒューズビットが設定されていない場合、PC6はリセット入力として使用されます。一定時間以上のパルス幅のLowレベルを端子に与えると、CPUクロックがないときであってもリセット状態となります。リセット信号の最小パルス幅については、Table28-3 (p.306)に記載されています。短すぎるパルスではリセット状態になることが保証されません。

ポートDは、内部にプルアップ抵抗(ビットごとに選択可能)を備えた8ビットの双方向入出力ポートです。ポートDの出力バッファは大きなシンク電流とソース電流を流すことができる対称的ドライブ能力をもっています。入力として使用するとき、外部でLowにプルダウンされている端子がプルアップ抵抗を有効にしていると、端子からソース電流が流れます。ポートDは、CPUクロックがない場合であってもリセット状態では、ハイ・インピーダンス状態になります。

ポートDの様々な特殊機能については、「ポートDの機能切り替え」 (p.83)に詳細が記載されています。

AVCCはA/Dコンバーター、PC3:0およびADC7:6の供給電源です。ADCを使用していない場合であっても外部でVCCに接続してください。ADCを使用する場合には、ローパス・フィルターを介してVCCに接続してください。PC6..4にはデジタル回路の供給電源VCCが使用されていることに注意してください。

AREFは、A/Dコンバーターのアナログ参照電圧端子です。

TQFPとQFN/MLFパッケージでは、ADC7:6はA/Dコンバーターのアナログ入力端子となります。これらの端子はアナログ供給電源を使用して10ビットADCチャンネルとして動作します。