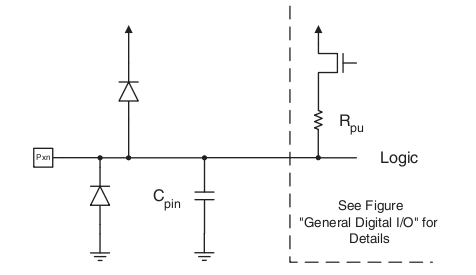

Figure 13-1. 入出力端子等価回路

AVRマイコンのすべてのポートは、汎用デジタルI/Oポートとして使用する場合、完全なリード・モディファイ・ライト機能を備えています。これは、ポートの入出力方向を、SBI、CBI命令によって、意図していない他の端子の入出力方向に影響を与えずに変更可能であることを意味します。出力値を変更するとき(出力として設定されている場合)、および、プルアップ抵抗を有効化・無効化する場合(入力として設定されている場合)にも、同じことがあてはまります。各出力バッファは大きなシンク電流とソース電流を駆動可能な対称的ドライブ能力を備えています。各端子のドライバーはLED表示器を直接ドライブするのに十分な力をもっています。すべてのポートの端子には、供給電圧に関係なく一定の抵抗値の、端子ごとに選択可能なプルアップ抵抗があります。すべての入出力端子には、Figure 13-1にあるとおり、VccとGNDにつながった保護ダイオードがついています。回路定数の一覧については、「電気的特性」(p.302)を参照してください。

このセクションでは、すべてのレジスタと各ビットの名称は、一般化された形式で記されています。小文字の"x"はポート番号を表すアルファベットを、小文字の"n"はビット番号を表しています。プログラム中で各レジスタやビットの定義を用いる場合は、正しい形式を使用しなければなりません。例えば、PORTBのビット3を表す"PORTB3"は、一般化した形式で"PORTxn"と記載されています。入出力レジスタのアドレスと各ビットの配置については、「レジスタ詳細」(p.86)に一覧があります。

それぞれのポートには三つのI/Oメモリアドレス、すなわちデータレジスタ PORTx、データ方向レジスタ DDRx、そしてポート入力ピン PINx、が割り当てられています。ポート入力ピンのI/Oアドレスは読み取り専用ですが、データレジスタおよびデータ方向レジスタは読み書きともに可能です。ただし、PINxレジスタに論理値1を書き込むことで、対応するデータレジスタのビットの値がトグル(反転)します。また、プルアップ無効ビット(MCUCRレジスタのPUDビット)をセットすると、すべてのポートのすべての端子のプルアップ機能が無効になります。

I/Oポートを汎用デジタル入出力としてつかう方法は、「汎用デジタル入出力としてのポート」(p.71)に記載されています。ほぼ全てのポートの端子は、デバイス上の周辺回路の他の機能と同一の端子に重複して割り当てられています。各機能を切り替えて使用する場合に、どのポートのどの端子と衝突するかについては、「ポートの機能切り替え」(p.75)に記載されています。同一端子上で切り替えて使用する機能のすべての内容については、個別のモジュールについてのセクションを参照してください。なお、あるポートの端子を他の機能に切り替えて使用しても、汎用デジタル入出力として使用している同一ポート内の他の端子には影響はありません。

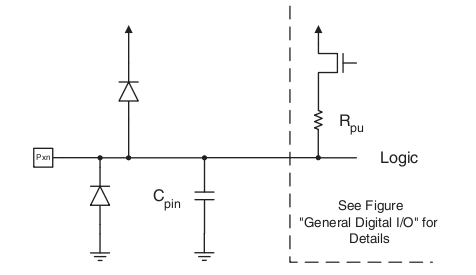

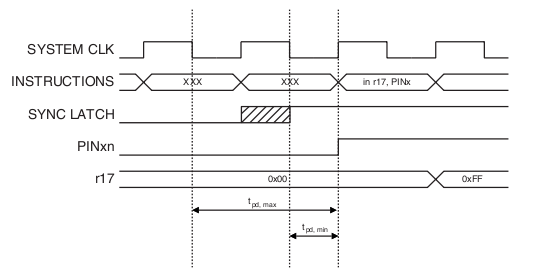

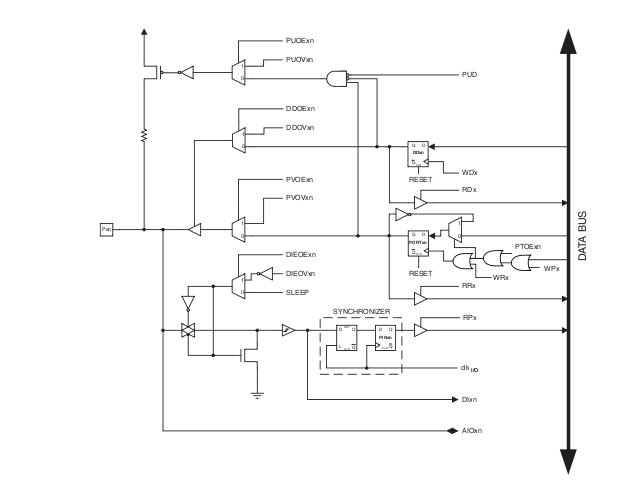

各ポートは双方向の入出力ポートで、切り離し可能な内蔵プルアップ機能を備えています。Figure 13-2に入出力ポートの一つの端子(ここでは一般化した表記でPxnとします)に備わっている機能について記します。

注意

1. WRx, WPx, WDx, RRx, RPx, および RDx は、すべての端子について同一ポート上では共通。

clkI/O, SLEEP, および PUD はすべてのポートで共通。

ポートの各端子は、三つのレジスタのビット、DDxn、PORTxn、PINxnによって構成されています。「レジスタ詳細」(p.86)にあるとおり、DDxnビットはDDRxレジスタのI/Oアドレスで、PORTxnビットはPORTxレジスタのI/Oアドレスで、そしてPINxnビットはPINxレジスタのI/Oアドレスで、アクセスします。

DDRxレジスタのDDxnビットは該当する端子の入出力方向を選択します。DDxnビットに論理値1が書き込まれているとき、Pxn端子は出力端子として設定されます。DDxnビットに論理値0が書き込まれていれば、Pxn端子は入力端子として設定されます。

入力端子として設定されているPORTxnビットに論理値1を書き込むと、プルアップ抵抗が有効になります。プルアップ抵抗を切り離すには、PORTxnビットに論理値0を書き込むか、出力端子として設定しなければなりません。リセット状態となったときは、CPUクロックが全くない状態であっても、ポートの端子はハイ・インピーダンス状態に設定されています。

出力端子として設定されているPORTxnビットに論理値1を書き込むと、該当するポートの端子がHi(1)になります。出力端子として設定されているPORTxnビットに論理値0を書き込むと、該当するポートの端子がLow(0)になります。

PINxnビットに論理値1を書き込むと、DDRxnビットの値に関係なく、PORTxnビットの値が反転します。SBI命令を用いて、ポートの1ビットのみを反転できるということです。

ハイ・インピーダンス状態 ({DDxn, PORTxn} = 0b00) とHi出力状態 ({DDxn, PORTxn} = 0b11) を切り替えるとき、プルアップ抵抗が有効な状態 ({DDxn, PORTxn} = 0b01) 、またはLow出力状態 ({DDxn, PORTxn} = 0b10) を経由しなければなりません。ハイ・インピーダンスの回路では、Hiに強くドライブされている状態とプルアップ状態との違いは動作に影響がないので、通常は全く問題ありません。もし、問題がある場合は、MCUCRレジスタのPUDビットをセットして全てのプルアップ抵抗を全ポートの端子で無効にすることができます。

プルアップが有効な入力状態とLow出力状態を切り替える場合にも同じ問題が生じます。ハイ・インピーダンス状態 ({DDxn, PORTxn} = 0b00) 、またはHi出力状態 ({DDxn, PORTxn} = 0b11) のいずれかを、中間的な状態として使用しなければなりません。

Table 13-1 に、端子の状態を制御する信号についてまとめます。

Table 13-1. ポートの端子設定

| DDxn | PORTxn | PUD (MCUCRレジスタ内) | 入出力 | プルアップ抵抗 | コメント |

|---|---|---|---|---|---|

| 0 | 0 | X | 入力 | なし | 3ステート (ハイ・インピーダンス) |

| 0 | 1 | 0 | 入力 | あり | Lowに接続されていると、Pxnからソース電流が流れます |

| 0 | 1 | 1 | 入力 | なし | 3ステート (ハイ・インピーダンス) |

| 1 | 0 | X | 出力 | なし | Low出力(シンク) |

| 1 | 1 | X | 出力 | なし | Hi出力(ソース) |

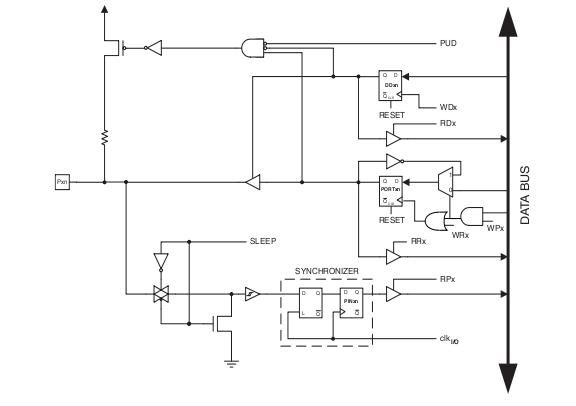

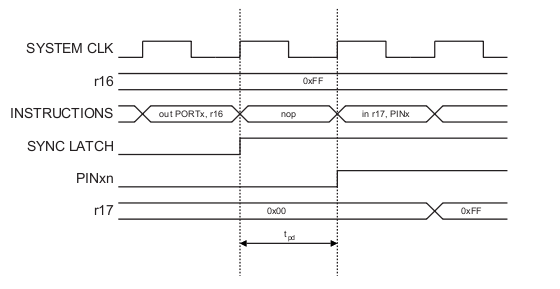

データ方向レジスタのビットDDxnの設定に関係なく、ポートの端子の状態を、PINxnレジスタのビットから読み取ることが可能です。Figure 13-2に示されている通り、PINxnレジスタのビット値と、その前段のラッチにより同期式の回路が構成されています。この回路は、実際の端子にかかる電圧が内部クロックのエッジ付近で変化した場合に不安定になるのをさけるために必要なものですが、同時に遅延が生じます。Figure 13-3に、外部端子の論理値を読み取る際の、同期動作のタイミング・ダイアグラムを示します。最大、および最小伝達遅延時間が、それぞれ、tpd,max、および tpd,minで示されています。

システム・クロックの最初の立ちさがり直後のクロック周期について考察してみましょう。クロックがLowの時はラッチは閉鎖されており、クロックがHi("SYNC LATCH"信号の影のついている部分で示されている)のとき透過状態となります。入力信号の値はシステム・クロックがLowになるとき、ラッチされ、それに続くクロックの立ち上がりエッジでPINxnレジスタに入力されます。二つの矢印、 tpd,max と tpd,min、で示されるように、1回の信号伝達は、入力信号の変化のタイミングによって0.5ないし1.5システム・クロック時間、遅延することになります。

ソフトウェアによって変更された端子の論理値を再度読み取る場合、Figure 13-4に示す通り、NOP命令を挿入する必要があります。OUT命令は、システム・クロックの立ち上がりエッジで "SYNC LATCH" 信号をセットします。この場合、同期回路を通しての伝達遅延時間tpdは、1システム・クロック時間となります。

下記のコーディング例では、ポートBの端子0と端子1をHiに、端子2と端子3をLowに、端子4から端子7までを入力とし、端子6と端子7でプルアップ抵抗を有効にする方法を表しています。設定後、端子の論理値を読み取っていますが、さきに説明したとおり、直前に設定された端子の値を読み取ることができるように、NOP命令が含まれています。

Assembly Code Example(1)

...

; プルアップするビット、Hi出力のビットを設定

; ポート端子の入出力方向を設定

ldi r16,(1<<PB7)|(1<<PB6)|(1<<PB1)|(1<<PB0)

ldi r17,(1<<DDB3)|(1<<DDB2)|(1<<DDB1)|(1<<DDB0)

out PORTB,r16

out DDRB,r17

; 同期のため、NOP命令を挿入

nop

; ポート端子を読み取る

in r16,PINB

...

C Code Example

unsigned char i;

...

/* プルアップするビット、Hi出力のビットを設定 */

/* ポート端子の入出力方向を設定 */

PORTB = (1<<PB7)|(1<<PB6)|(1<<PB1)|(1<<PB0);

DDRB = (1<<DDB3)|(1<<DDB2)|(1<<DDB1)|(1<<DDB0);

/* 同期のため、NOP命令を挿入 */

__no_operation();

/* ポート端子を読み取る */

i = PINB;

...

注意:

1. アセンブリ言語では、端子0、1、6、7のプルアップを有効にしてから、データ方向ビットを正しく設定して、ビット2とビット3をLowに、ビット0とビット1を強いHi状態にするまでの時間を最小化するため、二つのレジスタを一時的に使用しています。

Figure 13-2に示すとおり、デジタル入力信号はシュミット・トリガー・ゲートの入力の箇所でグラウンドにクランプできるようになっています。図中のSLEEPと記された信号は、パワーダウン・モード、パワーセーブ・モード、スタンバイ・モードにおいて、MCUスリープ・コントローラーによりセットされ、入力がフロート状態やVCC/2に近い状態のときに大きな電力が消費されるのを防止します。

SLEEP信号は、外部割り込み端子として有効になっているポートの端子に対しては無効になっています。外部割り込み要求が無効の場合も、SLEEP信号は当該の端子で有効になります。また、SLEEP信号に対しては、「ポート機能の切り替え」(p.75)にあるとおり、様々な他の切り替え機能が優先される場合があります。

「端子電圧の立ち上がりエッジ、たち下がりエッジ、またはあらゆる論理値の変化による割り込み」として設定された非同期の外部割り込み端子に、論理Hiレベル(論理値1)が印加されている状態で、外部割り込みが無効になっていると、上記に述べたスリープ・モードから復帰するときに、このスリープ・モードのクランプ回路により、要求されている論理変化が発生し、対応する外部割り込みフラグがセットされます。

使われていない端子がある場合には、それらの端子が論理値として正しい電圧を保持するようにしておくことを推奨します。ほぼ全てのデジタル入力はディープ・スリープ・モードでは上記に述べたとおり無効化されていますが、それ以外のあらゆるモード(リセット・モード、アクティブ・モード、アイドル・モード)では入力端子が有効になっており、電流消費を減らす上で、入力端子をフロート状態のままにしておくのは避けるべきです。

未使用端子に有効な電圧がかかるようにする一番簡単な方法は、内部プルアップ抵抗を有効にすることです。この方法では、プルアップ抵抗はリセット状態の間は無効になります。リセット中の低消費電力が重要である場合、外部のプルアップまたはプルダウン抵抗を使用することを推奨します。未使用端子を直接VCCやGNDに接続することは推奨しません。なぜなら、もし、その端子が何かの間違いで出力に設定されると、過大電流が流れるかもしれないからです。

ポートのほとんどの端子は、汎用デジタル入出力としてのほかに、他の切り替えて使用する機能が備わっています。Figure 13-5の図は、Figure 13-2に示した端子制御信号を、どのようにして他の機能に切り替えているかを、もう少し詳しく示しています。切り替え信号は全てのポートの端子に必ずしも備わっていないかもしれませんが、この図は、AVRマイコン・ファミリーの全ポートの端子について、一般的な構造を示すものといえます。

注意:1. WRx, WPx, WDx, RRx, RPx, および RDx は同一ポート上の全ての端子について共通。

clkI/O, SLEEP, および PUD は全ポートについて共通。その他全ての信号は各端子固有のもの。

Table 13-2に、機能切り替えの優先信号についてまとめます。Figure 13-5中の、端子とポートの添字はこの表では記されていません。優先信号は、切り替えて使用する端子に接続されるモジュール内部で生成されます。

Table 13-2. 機能切り替えの優先信号についての一般的な内容

| 信号 | 信号の名称 | 内容 |

|---|---|---|

| PUOE | Pull-up Override Enable | この信号がセットされると、PUOV信号の値にしたがってプルアップ抵抗が有効になります。クリア状態では、{DDxn, PORTxn, PUD} = 0b010 のとき、プルアップ抵抗が有効になります。 |

| PUOV | Pull-up Override Value | PUOEがセットされると、DDxn, PORTxn, PUDの値に関係なく、PUOV信号が「セット/クリア」状態で、プルアップ抵抗が「あり/なし」となります。 |

| DDOE | Data Direction Override Enable | この信号がセットされると、DDOV信号にしたがって出力ドライバ・イネーブル信号が制御されます。クリア状態のときは、出力ドライバはDDxnビットにより有効になります。 |

| DDOV | Data Direction Override Value | DDOEがセットされているとき、DDxnビットの値に関係なく、DDOVの値が「セット/クリア」状態で、出力ドライバが「有効/無効」になります。 |

| PVOE | Port Value Override Enable | この信号がセットされており、出力ドライバが有効の場合、端子の論理値はPVOV信号によって制御されます。PVOEがクリアされており、出力ドライバが有効の場合、端子の値はPORTxnビットの値となります。 |

| PVOV | Port Value Override Value | PVOEがセットされているとき、PORTxnビットの値に関係なく、端子の論理値がPVOVにセットされます。 |

| PTOE | Port Toggle Override Enable | PTOEがセットされると、PORTxnビットの値が反転します。 |

| DIEOE | Digital Input Enable Override Enable | このビットがセットされていると、デジタル入力の有効/無効はDIEOV信号によって制御されます。クリアされていると、デジタル入力の有効/無効はMCUの状態(ノーマル・モード、スリープ・モード)によって決まります。 |

| DIEOV | Digital Input Enable Override Value | このビットがセットされていると、デジタル入力の「有効/無効」は、MCUの状態(ノーマル・モード、スリープ・モード)に関係なく、DIEOVが「セット/クリア」で決まります。 |

| DI | Digital Input | 他の機能モジュールへのデジタル入力。図中では、この信号はシュミット・トリガー・ゲートの出力に同期回路の前で接続されています。デジタル入力がクロック源として使用されている場合をのぞいて、機能切り替えで使用される各モジュールは独自の同期回路を用いています。 |

| AIO | Analog Input/Output | 他の機能モジュールのアナログ入出力に接続。この信号は、直接端子につながっており、入出力双方向で使用されます。 |

以下のサブ・セクションでは各ポートの機能切り替え、および機能切り替えの優先信号について、簡潔にまとめています。より詳細については、切り替えて使用する各機能の項目を参照してください。

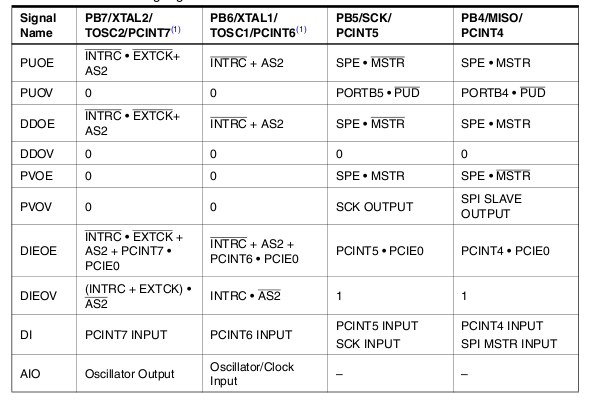

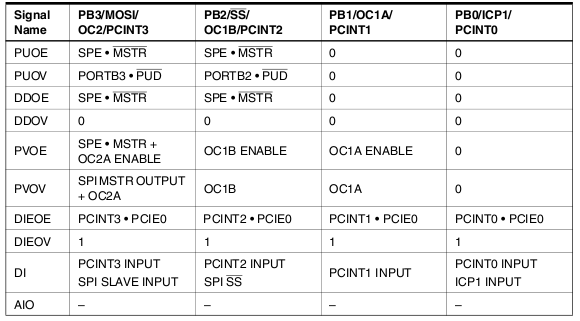

ポートBの各端子の機能切り替えについて、Table13-3に記します。

Table 13-3. ポートB端子の機能切り替え

| 端子 | 切り替え可能な機能 | |||||

|---|---|---|---|---|---|---|

| PB7 |

|

|||||

| PB6 |

|

|||||

| PB5 |

|

|||||

| PB4 |

|

|||||

| PB3 |

|

|||||

| PB2 |

|

|||||

| PB1 |

|

|||||

| PB0 |

|

端子の機能切り替えについては以下のとおりです。

クロック発振器端子2。水晶発振器または、低周波水晶発振器のクロック端子として使用され、入出力端子として使用することは出来ません。外部クロックがXTAL1に接続されている場合は、この端子を入出力端子として使用可能です。

タイマー発信器端子2。キャリブレート済み内蔵RC発振器がチップ・クロック源として選択され、非同期タイマーがASSRレジスタにより正しく設定され有効になっている場合のみ使用されます。ASSRレジスタのAS2ビットがセットされ(1)、EXCLKビットがクリアされている(0)とき、タイマー/カウンター2の水晶発振器を使った非同期クロックが有効になり、PB7端子はポートから切り離され、発振器アンプの反転出力として動作します。このモードでは、水晶発振器が端子に接続されており、入出力として使用することはできません。

ピン・チェンジ割り込みソース7。PB7端子は外部割り込み端子として使用できます。PB7がクロック端子として使用されている場合は、DDB7、PORTB7、およびPINB7は全て読み取り時に0となります。

クロック発振器端子1。キャリブレート済み内蔵RC発振器以外の、全てのチップ・クロック源で使用されます。クロック端子として使用されている場合、入出力端子として使用することは出来ません。

タイマー発信器端子1。キャリブレート済み内蔵RC発振器がチップ・クロック源として選択され、非同期タイマーがASSRレジスタにより正しく設定され有効になっている場合のみ使用されます。ASSRレジスタのAS2ビットがセットされ(1)ているとき、タイマー/カウンター2の水晶発振器を使った非同期クロックが有効になり、PB6端子はポートから切り離され、発振器アンプの入力端子として動作します。このモードでは、水晶発振器が端子に接続されており、入出力として使用することはできません。

ピン・チェンジ割り込みソース6。PB6端子は外部割り込み端子として使用できます。PB6がクロック・端子として使用されている場合は、DDB6、PORTB6、およびPINB6は全て読み取り時に0となります。

SPIのクロック・アウト(マスター)/クロック・イン(スレーブ)。

SPIがスレーブ動作のとき、データ方向ビットDDBレジスタのビット5の値に関係なく、この端子は入力として設定されます。SPIがマスター動作の時、この端子のデータ方向はDDBレジスタのビット5の値で決まります。SPIの動作により、この端子が強制的に入力として使用されるときでも、プルアップはPORTBレジスタのビット5によってオン・オフ可能です。

ピン・チェンジ割り込みソース5。PB5端子は外部割り込み端子として使用できます。

SPIのマスター・イン/スレーブ・アウト信号線。

SPIがマスター動作のとき、データ方向ビットDDBレジスタのビット4の値に関係なく、この端子は入力として設定されます。SPIがスレーブ動作の時、この端子のデータ方向はDDBレジスタのビット4の値で決まります。SPIの動作により、この端子が強制的に入力として使用されるときでも、プルアップはPORTBレジスタのビット5によってオン・オフ可能です。

ピン・チェンジ割り込みソース4。PB4端子は外部割り込み端子として使用できます。

SPIのマスター・アウト/スレーブ・イン信号線。

SPIがスレーブ動作のとき、データ方向ビットDDBレジスタのビット3の値に関係なく、この端子は入力として設定されます。SPIがマスター動作の時、この端子のデータ方向はDDBレジスタのビット3の値で決まります。SPIの動作により、この端子が強制的に入力として使用されるときでも、プルアップはPORTBレジスタのビット3によってオン・オフ可能です。

PB3 端子はタイマー/カウンター2のコンペア・マッチ信号の外部出力として使用できます。PB3端子をこの機能で使う場合は、出力端子として設定(DDBレジスタのビット3を1に)しておかなければなりません。OC2端子は、PWMモードのタイマーにおける出力端子でもあります。

ピン・チェンジ割り込みソース3。PB3端子は外部割り込み端子として使用できます。

| SS | /OC1B/PCINT2 – Port B, Bit 2 |

| SS | : |

スレーブ・セレクト入力。

SPIがスレーブ動作のとき、データ方向ビットDDBレジスタのビット2の値に関係なく、この端子は入力として設定されます。スレーブとして、SPIが有効になると、この端子はLowを出力します。マスターとしてSPIが動作しているとき、この端子のデータ方向はDDBレジスタのビット2の値で決まります。SPIの動作により、この端子が強制的に入力として使用されるときでも、プルアップはPORTBレジスタのビット2によってオン・オフ可能です。

PB2 端子はタイマー/カウンター1のコンペア・マッチB信号の外部出力として使用できます。PB2端子をこの機能で使う場合は、出力端子として設定(DDBレジスタのビット2を1に)しておかなければなりません。OC1B端子は、PWMモードのタイマーにおける出力端子でもあります。

ピン・チェンジ割り込みソース2。PB2端子は外部割り込み端子として使用できます。

PB1 端子はタイマー/カウンター1のコンペア・マッチA信号の外部出力として使用できます。PB1端子をこの機能で使う場合は、出力端子として設定(DDBレジスタのビット1を1に)しておかなければなりません。OC1A端子は、PWMモードのタイマーにおける出力端子でもあります。

ピン・チェンジ割り込みソース1。PB1端子は外部割り込み端子として使用できます。

PB0 端子はタイマー/カウンター1のインプット・キャプチャ端子として動作させることができます。

PB0端子に分周されたシステム・クロックを出力することができます。分周システム・クロックはCKOUTヒューズビット有効の状態でプログラムされているときに、PORTB0ビット、DDB0ビットの設定に関係なく、出力されます。この出力は、リセット中であっても有効です。

ピン・チェンジ割り込みソース0。PB0端子は外部割り込み端子として使用できます。

Table 13-4 および Table 13-5 はポートBの機能切り替えを、Figure 13-5 (p.75)中にある優先信号に関連付けて書いたものです。SPI MSTR INPUT および SPI SLAVE OUTPUT により MISO 信号が構成され、MOSI 信号は SPI MSTR OUTPUT と SPI SLAVE INPUTに分割されています。

注意

1. INTRC は、内蔵RC発振器のいずれかが(CKSELヒューズによって)選択されている状態、EXTCK は、外部クロックが(CKSELヒューズによって)選択されている状態

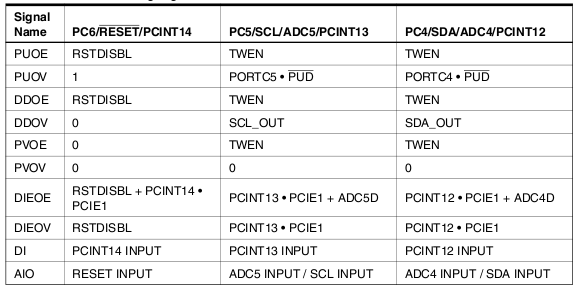

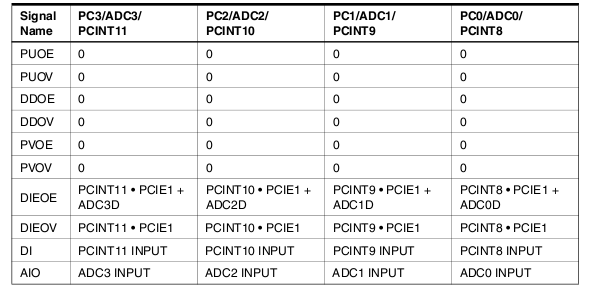

ポートCの各端子の機能切り替えについて、Table13-6に記します。

Table 13-6. ポートC端子の機能切り替え

| 端子 | 切り替え可能な機能 | ||||

|---|---|---|---|---|---|

| PC6 |

|

||||

| PC5 |

|

||||

| PC4 |

|

||||

| PC3 |

|

||||

| PC2 |

|

||||

| PC1 |

|

||||

| PC0 |

|

端子の機能切り替えについては以下のとおりです。

| RESET | /PCINT14 – Port C, Bit 6 |

| RESET | , リセット端子: |

RSTDISBLヒューズがプログラムされているとき、この端子は通常の入出力端子として機能し、デバイスのリセット手段は、パワーオン・リセットとブラウンアウト・リセットのみになります。RSTDISBLがプログラムされていないとき、リセット回路はこの端子に接続され、同端子を入出力に用いることはできなくなります。

PC6をリセット端子として使用しているとき、DDC6、PORTC6、PINC6のすべては読み取り時にゼロとなります。

ピン・チェンジ割り込みソース14。PC6端子は外部割り込み端子として使用できます。

TWCRレジスタのTWENビットがセット(1)されていると、2線式シリアル・インターフェースが有効になり、PC5端子はポートから切り離され、2線式シリアル・インターフェースのシリアル・クロック入出力端子となります。このモードでは、入力信号上の50nS以下のスパイク・ノイズを抑制するためのフィルターがあり、同端子はスルーレートを制限されたオープン・ドレイン出力となります。

PC5はA/Dコンバーターの入力チャンネル5としても使用できます。A/Dコンバーターの入力チャンネル5は、デジタル回路用の電源を使用していることに注意してください。

ピン・チェンジ割り込みソース13。PC5端子は外部割り込み端子として使用できます。

TWCRレジスタのTWENビットがセット(1)されていると、2線式シリアル・インターフェースが有効になり、PC4端子はポートから切り離され、2線式シリアル・インターフェースのシリアル・データ入出力端子となります。このモードでは、入力信号上の50nS以下のスパイク・ノイズを抑制するためのフィルターがあり、同端子はスルーレートを制限されたオープン・ドレイン出力となります。

PC4はA/Dコンバーターの入力チャンネル4としても使用できます。A/Dコンバーターの入力チャンネル4は、デジタル回路用の電源を使用していることに注意してください。

ピン・チェンジ割り込みソース12。PC4端子は外部割り込み端子として使用できます。

PC3はA/Dコンバーターの入力チャンネル3としても使用できます。A/Dコンバーターの入力チャンネル3は、アナログ回路用の電源を使用していることに注意してください。

ピン・チェンジ割り込みソース11。PC3端子は外部割り込み端子として使用できます。

PC2はA/Dコンバーターの入力チャンネル2としても使用できます。A/Dコンバーターの入力チャンネル2は、アナログ回路用の電源を使用していることに注意してください。

ピン・チェンジ割り込みソース10。PC2端子は外部割り込み端子として使用できます。

PC1はA/Dコンバーターの入力チャンネル1としても使用できます。A/Dコンバーターの入力チャンネル1は、アナログ回路用の電源を使用していることに注意してください。

ピン・チェンジ割り込みソース9。PC1端子は外部割り込み端子として使用できます。

PC0はA/Dコンバーターの入力チャンネル0としても使用できます。A/Dコンバーターの入力チャンネル0は、アナログ回路用の電源を使用していることに注意してください。

ピン・チェンジ割り込みソース8。PC0端子は外部割り込み端子として使用できます。

Table 13-7 および Table 13-8 はポートCの機能切り替えを、Figure 13-5 (p.75)中にある優先信号に関連付けて書いたものです。

注意:

1 2線式シリアル・インターフェースが有効になっていると、PC4およびPC5出力端子のスルーレート抑制が有効になります。これは、図中には記されていません。また、ポート構成図に描かれたAIO出力と端子間、およびTWIモジュールの回路と端子の間にはスパイク・ノイズ・フィルターが接続されています。

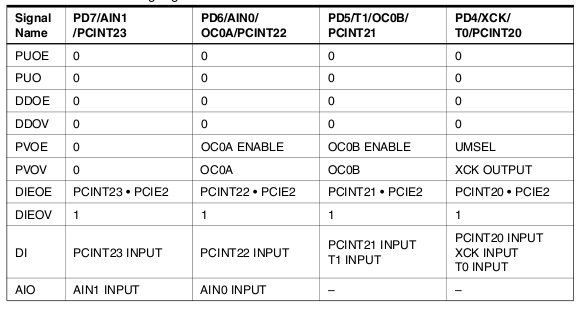

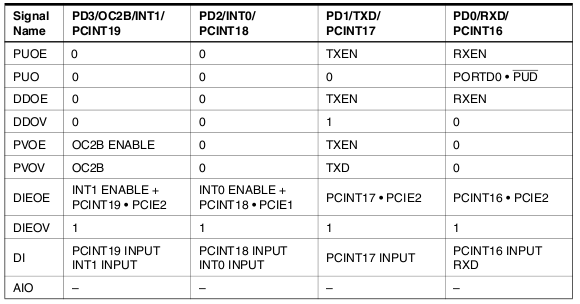

ポートDの各端子の機能切り替えについて、Table13-9に記します。

Table 13-9. ポートD端子の機能切り替え

| 端子 | 切り替え可能な機能 | |||

|---|---|---|---|---|

| PD7 |

|

|||

| PD6 |

|

|||

| PD5 |

|

|||

| PD4 |

|

|||

| PD3 |

|

|||

| PD2 |

|

|||

| PD1 |

|

|||

| PD0 |

|

端子の機能切り替えについては以下のとおりです。

この端子をアナログ・コンパレーター入力として使用する場合、デジタル・ポート機能との干渉を防ぐため、入力として設定し、プルアップ抵抗を無効にしてください。

ピン・チェンジ割り込みソース23。PD7端子は外部割り込み端子として使用できます。

この端子をアナログ・コンパレーター入力として使用する場合、デジタル・ポート機能との干渉を防ぐため、入力として設定し、プルアップ抵抗を無効にしてください。

PD6端子はタイマー/カウンター0 コンペア・マッチA信号の外部出力端子として使用できます。この機能を使うためには、PD6 端子を出力に設定(DDR6を1にセット)する必要があります。OC0A端子はタイマー機能のPWMモードにおける出力端子でもあります。

ピン・チェンジ割り込みソース22。PD6端子は外部割り込み端子として使用できます。

PD5端子はタイマー/カウンター0 コンペア・マッチB信号の外部出力端子として使用できます。この機能を使うためには、PD5 端子を出力に設定(DDR5を1にセット)する必要があります。OC0B端子はタイマー機能のPWMモードにおける出力端子でもあります。

ピン・チェンジ割り込みソース21。PD5端子は外部割り込み端子として使用できます。

ピン・チェンジ割り込みソース20。PD4端子は外部割り込み端子として使用できます。

PD3端子は外部割り込み入力として使用できます。

PD3端子はタイマー/カウンター2 コンペア・マッチB信号の外部出力端子として使用できます。この機能を使うためには、PD3 端子を出力に設定(DDR3を1にセット)する必要があります。OC2B端子はタイマー機能のPWMモードにおける出力端子でもあります。

ピン・チェンジ割り込み入力19。PD3端子は外部割り込み入力として使用できます。

PD2端子は外部割り込み入力として使用できます。

ピン・チェンジ割り込みソース18。PD2端子は外部割り込み端子として使用できます。

USART送信が有効になっているとき、この端子は、DD1の値に関係なく、出力として設定されます。

ピン・チェンジ割り込みソース17。PD1端子は外部割り込み端子として使用できます。

USART受信が有効になっているとき、この端子は、DD0の値に関係なく、入力として設定されます。USARTがこの端子を強制的に入力として使用する場合でも、PORTD0ビットによってプルアップ抵抗の設定が可能です。

ピン・チェンジ割り込みソース16。PD0端子は外部割り込み端子として使用できます。

Table 13-10 および Table 13-11 はポートDの機能切り替えを、Figure 13-5 (p.75)中にある優先信号に関連付けて書いたものです。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x35(0x55) | - | - | - | PUD | - | - | IVSEL | IVCE | MCUCR |

| Read/Write | R | R | R | R/W | R | R | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

このビットに1が書き込まれていると、DDxnおよびPORTxnレジスタがプルアップ抵抗を接続するように設定 ({DDxn, PORTxn} = 0b01)されていても、ポート入出力のプルアップ抵抗が無効になります。この機能の詳細については、「端子の機能を設定する」(p.71)を参照してください。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x05(0x25) | PORTB7 | PORTB6 | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTB0 | PORTB |

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x04(0x24) | DDB7 | DDB6 | DDB5 | DDB4 | DDB3 | DDB2 | DDB1 | DDB0 | DDRB |

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x03(0x23) | PINB7 | PINB6 | PINB5 | PINB4 | PINB3 | PINB2 | PINB1 | PINB0 | PINB |

| Read/Write | R | R | R | R | R | R | R | R | |

| 初期値 | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A |

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x08(0x28) | - | PORTC6 | PORTC5 | PORTC4 | PORTC3 | PORTC2 | PORTC1 | PORTC0 | PORTC |

| Read/Write | R | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x07(0x27) | - | DDC6 | DDC5 | DDC4 | DDC3 | DDC2 | DDC1 | DDC0 | DDRC |

| Read/Write | R | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x06(0x26) | - | PINC6 | PINC5 | PINC4 | PINC3 | PINC2 | PINC1 | PINC0 | PINC |

| Read/Write | R | R | R | R | R | R | R | R | |

| 初期値 | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A |

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x0B(0x2B) | PORTD7 | PORTD6 | PORTD5 | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTD0 | PORTD |

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x0A(0x2A) | DDD7 | DDD6 | DDD5 | DDD4 | DDD3 | DDD2 | DDD1 | DDD0 | DDRD |

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x09(0x29) | PIND7 | PIND6 | PIND5 | PIND4 | PIND3 | PIND2 | PIND1 | PIND0 | PIND |

| Read/Write | R | R | R | R | R | R | R | R | |

| 初期値 | N/A | N/A | N/A | N/A | N/A | N/A | N/A | N/A |