外部割込みは、INT0、INT1およびPCINT23..0のいずれかの端子により発生します。外部割込みが有効になっていれば、INT0、INT1、PCINT23..0端子が出力として設定されている場合であっても、割込みが発生することに注意してください。この機能によって、ソフトウェア割込みを発生させることができます。ピン・チェンジ割込みPCI2は、有効であれば、PCINT23..16の端子のいずれかの値の反転によって発生します。ピン・チェンジ割込みPCI1は、有効であれば、PCINT14..8の端子のいずれかの値の反転により発生します。ピン・チェンジ割込みPCI0は、有効であれば、PCINT7..0の端子のいずれかの値の反転により発生します。PCMSK2、PCMSK1、PCMSK0レジスタによって、どの端子がピン・チェンジ割込みの要因となるかを制御します。PCINT23..0端子によるピン・チェンジ割込みは、非同期動作により検出され、発生します。このことは、これらの割込みにより、アイドル・モード以外のスリープ・モードからウェークアップするために使用可能であることを意味します。

INT0およびINT1割込みは、エッジの立ち下がり、立ち上がり、あるいはLowレベル状態により発生させることができます。外部割込みコントロール・レジスタA(EICRA)の説明にあるとおりに設定することで可能です。INT0あるいはINT1割込みが有効になっていて、電圧レベルによって割込みを発生するように設定されている場合、その端子がLow状態に保持されている期間にわたって割込みが発生します。INT0あるいはINT1のエッジの立ち下がり、立ち上がり検出には、「クロック・システムとその配分」(p.26)に説明されているとおり、I/Oクロックが動作している必要があります。INT0あるいはINT1のLowレベル割込みは、非同期動作により検出されます。このことは、これらの割込みにより、アイドル・モード以外のスリープ・モードからウェークアップするために使用可能であることを意味します。I/Oクロックは、アイドル・モード以外のスリープ・モードでは停止しています。

パワーダウン・モードからのウェークアップにレベル検出による割込みを使用する場合、MCUがウェークアップ動作を行い、レベル検出による割込みを発生させるために十分長い時間にわたり検出に必要な電圧レベルが保持されていなければなりません。必要な電圧レベルがスタート・アップ時間が終了する前になくなってしまった場合、MCUはウェークアップ動作は行いますが、割込みは発生しません。「システム・クロックとクロックのオプション」(p.26)に説明されているように、スタート・アップ時間は、SUTおよびCKSELヒューズ・ビットにより設定されます。

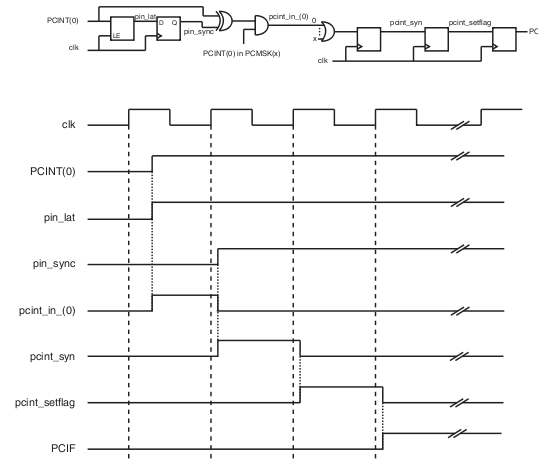

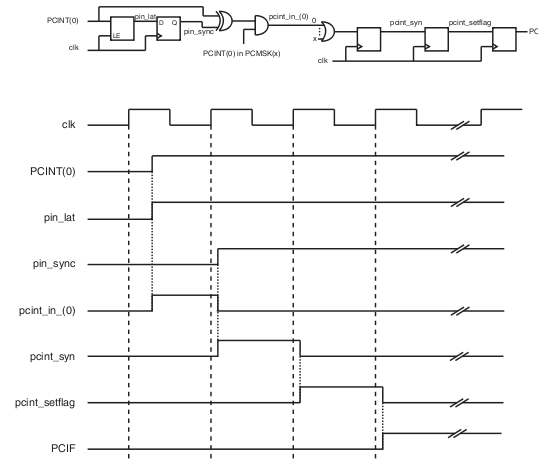

Figure 12-1に、ピン・チェンジ割込みのタイミングの例が示されています。

Figure 12-1. ピン・チェンジ割込みのタイミング

外部割込みコントロール・レジスタAには、割込み検出のための制御ビットがあります。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x69) | - | - | - | - | ISC11 | ISC10 | ISC01 | ISC00 | EICRA |

| Read/Write | R | R | R | R | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

これらのビットはATmega48/88/168では未使用であり、読み出し時には常にゼロになります。

外部割込み1は、SREGのIビットおよび該当する割込みマスクビットがセットされている場合、外部端子INT1によって発生します。Table 12-1に、INT1端子の電圧変化やエッジの検出の、どれにより割込みを発生するかが記載されています。INT1端子の値は検出するエッジの直前でサンプリングされます。エッジまたは値反転による割込みが選択されている場合、1クロック期間よりも長い時間継続するパルスに対して割込みが発生します。それよりも短い時間のパルスでの割込み発生動作は保証されません。Lowレベル値による割込み発生が選択されている場合、割込みが発生するためには、その時点で実行中の命令の動作完了までLowレベル値が保持されている必要があります。

Table 12-1. 割込み1 検出コントロール

| ISC11 | ISC10 | 機能 |

|---|---|---|

| 0 | 0 | INT1のLowレベル値によって割込みが発生 |

| 0 | 1 | INT1の論理値反転によって割込みが発生 |

| 1 | 0 | INT1の立ち下がりエッジによって割込みが発生 |

| 1 | 1 | INT1の立ち上がりエッジによって割込みが発生 |

外部割込み0は、SREGのIビットおよび該当する割込みマスクビットがセットされている場合、外部端子INT0によって発生します。Table 12-2に、INT0端子の電圧変化やエッジの検出の、どれにより割込みを発生するかが記載されています。INT0端子の値は検出するエッジの直前でサンプリングされます。エッジまたは値反転による割込みが選択されている場合、1クロック期間よりも長い時間継続するパルスに対して割込みが発生します。それよりも短い時間のパルスでの割込み発生動作は保証されません。Lowレベル値による割込み発生が選択されている場合、割込みが発生するためには、その時点で実行中の命令の動作完了までLowレベル値が保持されている必要があります。

Table 12-2. 割込み0 検出コントロール

| ISC01 | ISC00 | 機能 |

|---|---|---|

| 0 | 0 | INT0のLowレベル値によって割込みが発生 |

| 0 | 1 | INT0の論理値反転によって割込みが発生 |

| 1 | 0 | INT0の立ち下がりエッジによって割込みが発生 |

| 1 | 1 | INT0の立ち上がりエッジによって割込みが発生 |

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x1D (0x3D) | - | - | - | - | - | INT1 | INT0 | EIMSK | EIMSK |

| Read/Write | R | R | R | R | R | R | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

これらのビットはATmega48/88/168では未使用であり、読み出し時には常にゼロになります。

INT1ビットがセット(1)されていて、かつ、ステータス・レジスタ(SREG)のIビットがセット(1)されているとき、外部端子による割込みが有効になっています。外部割込みコントロール・レジスタA(EICRA)の割込み検出コントロール1・ビット1/0(ISC11とISC10)の設定により、INT1端子の立ち上がりエッジ、立ち下がりエッジ、その両方のエッジ、あるいは電圧レベルによる検出の、どの方法によって外部割込みが発生するかが決まります。INT1端子におけるレベル変化は、INT1端子が出力として設定されている場合であっても、割込み発生要因となります。これに対応する割込みとして、INT1割込みベクトルで始まる、外部割込みリクエスト1割込み処理が実行されます。

INT0ビットがセット(1)されていて、かつ、ステータス・レジスタ(SREG)のIビットがセット(1)されているとき、外部端子による割込みが有効になっています。外部割込みコントロール・レジスタA(EICRA)の割込み検出コントロール0・ビット1/0(ISC01とISC00)の設定により、INT0端子の立ち上がりエッジ、立ち下がりエッジ、その両方のエッジ、あるいは電圧レベルによる検出の、どの方法によって外部割込みが発生するかが決まります。INT0端子におけるレベル変化は、INT0端子が出力として設定されている場合であっても、割込み発生要因となります。これに対応する割込みとして、INT0割込みベクトルで始まる、外部割込みリクエスト1割込み処理が実行されます。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x1C (0x3C) | - | - | - | - | - | - | INTF1 | INTF0 | EIFR |

| Read/Write | R | R | R | R | R | R | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

これらのビットはATmega48/88/168では未使用であり、読み出し時には常にゼロになります。

INT1端子でのエッジまたは値の変化により割込みが発生する際に、INTF1ビットがセット(1)されます。SREGのIビット、および、EIMSKレジスタのINT1ビットがセットされている場合、MCUは対応する割込みベクトルへジャンプします。割込み処理ルーチンが実行されると、このフラグはクリアされます。別の方法として、このフラグに1を書き込むことでクリアすることもできます。このフラグはINT1端子がレベル検出による割込みを設定されている場合は常にクリア状態となります。

INT0端子でのエッジまたは値の変化により割込みが発生する際に、INTF0ビットがセット(1)されます。SREGのIビット、および、EIMSKレジスタのINT0ビットがセットされている場合、MCUは対応する割込みベクトルへジャンプします。割込み処理ルーチンが実行されると、このフラグはクリアされます。別の方法として、このフラグに1を書き込むことでクリアすることもできます。このフラグはINT1端子がレベル検出による割込みを設定されている場合は常にクリア状態となります。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x1C (0x3C) | - | - | - | - | - | PCIE2 | PCIE1 | PCIE0 | PCICR |

| Read/Write | R | R | R | R | R | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

これらのビットはATmega48/88/168では未使用であり、読み出し時には常にゼロになります。

PCIE2ビットがセット(1)されていて、かつ、ステータス・レジスタ(SREG)のIビットがセット(1)されているとき、ピン・チェンジ割込み2が有効になります。有効と設定されたPCINT23..16端子のいずれかでレベル変化があると、割込みが発生します。これに対応する割込みとして、PCI2割込みベクトルで始まる、ピン・チェンジ割込みリクエストが発生します。PCINT23..16端子は、PCMSK2レジスタにより個別に有効/無効の設定ができます。

PCIE1ビットがセット(1)されていて、かつ、ステータス・レジスタ(SREG)のIビットがセット(1)されているとき、ピン・チェンジ割込み1が有効になります。有効と設定されたPCINT14..8端子のいずれかでレベル変化があると、割込みが発生します。これに対応する割込みとして、PCI1割込みベクトルで始まる、ピン・チェンジ割込みリクエストが発生します。PCINT14..8端子は、PCMSK1レジスタにより個別に有効/無効の設定ができます。

PCIE0ビットがセット(1)されていて、かつ、ステータス・レジスタ(SREG)のIビットがセット(1)されているとき、ピン・チェンジ割込み0が有効になります。有効と設定されたPCINT7..0端子のいずれかでレベル変化があると、割込みが発生します。これに対応する割込みとして、PCI0割込みベクトルで始まる、ピン・チェンジ割込みリクエストが発生します。PCINT7..0端子は、PCMSK0レジスタにより個別に有効/無効の設定ができます。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x1B (0x3B) | - | - | - | - | - | PCIF2 | PCIF1 | PCIF0 | PCIFR |

| Read/Write | R | R | R | R | R | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

これらのビットはATmega48/88/168では未使用であり、読み出し時には常にゼロになります。

PCINT23..16端子のいずれかでのレベル変化により割込みが発生する際に、PCIF2ビットがセット(1)されます。SREGのIビットとPCICRレジスタのPCIE2ビットがセット(1)されている場合、MCUは対応する割込みベクトルへとジャンプします。割込み処理ルーチンが実行されると、このフラグはクリアされます。別の方法として、このフラグに1を書き込むことでクリアすることもできます。

PCINT14..8端子のいずれかでのレベル変化により割込みが発生する際に、PCIF1ビットがセット(1)されます。SREGのIビットとPCICRレジスタのPCIE1ビットがセット(1)されている場合、MCUは対応する割込みベクトルへとジャンプします。割込み処理ルーチンが実行されると、このフラグはクリアされます。別の方法として、このフラグに1を書き込むことでクリアすることもできます。

PCINT7..0端子のいずれかでのレベル変化により割込みが発生する際に、PCIF0ビットがセット(1)されます。SREGのIビットとPCICRレジスタのPCIE0ビットがセット(1)されている場合、MCUは対応する割込みベクトルへとジャンプします。割込み処理ルーチンが実行されると、このフラグはクリアされます。別の方法として、このフラグに1を書き込むことでクリアすることもできます。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x6D) | PCINT23 | PCINT22 | PCINT21 | PCINT20 | PCINT19 | PCINT18 | PCINT17 | PCINT16 | PCMSK2 |

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

PCINT23..16の各ビットにより、どのピン・チェンジ割込みをそれぞれが対応するI/O端子上で有効にするかを選択します。PCINT23..16がセットされていて、かつPCICRレジスタのPCIE2ビットがセットされている場合、ピン・チェンジ割込みが対応するI/O端子上で有効になります。PCINT23..16がクリアされている場合、対応するI/O端子上でのピン・チェンジ割込みは無効になります。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x6C) | - | PCINT14 | PCINT13 | PCINT12 | PCINT11 | PCINT10 | PCINT9 | PCINT8 | PCMSK1 |

| Read/Write | R | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

このビットはATmega48/88/168では未使用であり、読み出し時には常にゼロになります。

PCINT14..8の各ビットにより、どのピン・チェンジ割込みをそれぞれが対応するI/O端子上で有効にするかを選択します。PCINT14..8がセットされていて、かつPCICRレジスタのPCIE1ビットがセットされている場合、ピン・チェンジ割込みが対応するI/O端子上で有効になります。PCINT14..8がクリアされている場合、対応するI/O端子上でのピン・チェンジ割込みは無効になります。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x6B) | PCINT7 | PCINT6 | PCINT5 | PCINT4 | PCINT3 | PCINT2 | PCINT1 | PCINT0 | PCMSK0 |

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

PCINT7..0の各ビットにより、どのピン・チェンジ割込みをそれぞれが対応するI/O端子上で有効にするかを選択します。PCINT7..0がセットされていて、かつPCICRレジスタのPCIE0ビットがセットされている場合、ピン・チェンジ割込みが対応するI/O端子上で有効になります。PCINT7..0がクリアされている場合、対応するI/O端子上でのピン・チェンジ割込みは無効になります。