debugWIREオンチップ・デバッグシステムは、1-wire双方向インターフェースを用いて、プログラム・フローの制御、AVR命令のCPU上での実行、様々な不揮発メモリのプログラムを行います。

debugWIREイネーブル(DWEN)ヒューズがプログラム状態で、ロック・ビットがプログラムされていない場合、ターゲット・デバイスのdebugWIREシステムが有効になります。 RESET端子は、ワイアードAND(オープン・ドレイン)でプルアップ有効の双方向I/O端子として設定され、ターゲットとエミュレータの通信ゲートウェイとなります。

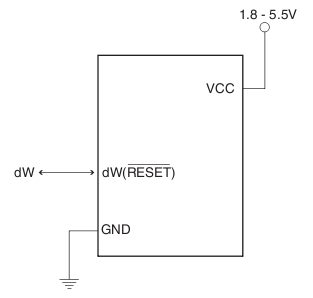

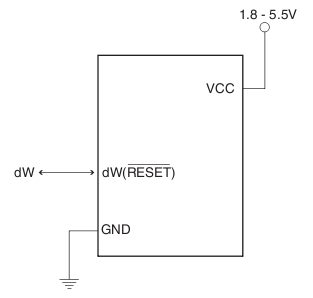

Figure 24-1. debugWIREのセットアップ

Figure 24-1に、debugWIREが有効になっているターゲットMCUとエミュレーター・コネクタの回路図を示します。 debugWIREによるシステム・クロックへの影響はなく、常にCKSELフューズによりクロック源が選択されます。

debugWIREを利用するシステムを設計する際には、正常な動作を行うために下記の点に注意する必要があります

debugWIREでは、AVRのBreak命令による、プログラムメモリ上でのブレークポイント設定をサポートします。 AVR Studio(R)でブレークポイントの設定を行うと、プログラムメモリにBreak命令が挿入されます。 Break命令を上書きされたアドレスの命令は他の場所に保管されます。 プログラムの実行を再スタートさせる際に、まず保管されていた命令が実行され、プログラムメモリ上での実行が再開されます。 手作業でBreak命令をプログラム中に書きこんで、プログラムを中断させることもできます。

ブレークポイントを再設定する際には、毎回フラッシュメモリの再プログラムをすることになります。 この操作は、debugWIREインターフェースによりAVR Studioが自動で行います。 したがって、ブレークポイントの使用により、フラッシュメモリのデータ保持期間が減少することになります。 デバッグに用いたデバイスをエンドユーザー向けに出荷するべきではありません。

debugWIREの通信を行う端子(dW)は、外部リセット端子(RESET)と同一の端子に割り当てられています。 したがって、debugWIREを有効に設定している場合、外部リセットは使用できません。

debugWIREシステムはSPIモジュールと同じシステム・クロックを使用します。 したがって、デバッグを行う際には、PRRレジスタのPRSPIビットをセットしないでください。 PRSPIビットをセットするとdebugWIREモジュールへのクロックが供給されなくなり、デバイスがロックされ使用できなくなる場合があります。

DWENヒューズビットをプログラム状態にすると、一部のクロックシステムは、スリープモードの状態に関係なく、常に動作し続けるようになります。 このためスリープ時の消費電力が増加することになります。 したがって、debugWIREを使用しない場合は、DWENヒューズビットを無効にしておいてください。

以下に、debutWIREの使用に関連するレジスタについて説明します。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| DWDR[7:0] | DWDR | ||||||||

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

DWDRレジスタは、MCU内で実行中のプログラムからデバッガへの通信経路として機能します。 このレジスタはdebugWIREによってのみアクセス可能で、通常の動作において汎用レジスタとして使用することはできません。