ATmega48/88/168には、10ビットの逐次変換A/Dコンバータ(ADC)が搭載されています。 ADCには8チャンネルのアナログ・マルチプレクサが接続されており、8つのシングル・エンドのアナログ電圧をポートC端子から入力することができます。シングル・エンドの入力は、0V(GND)に対する電圧となります。

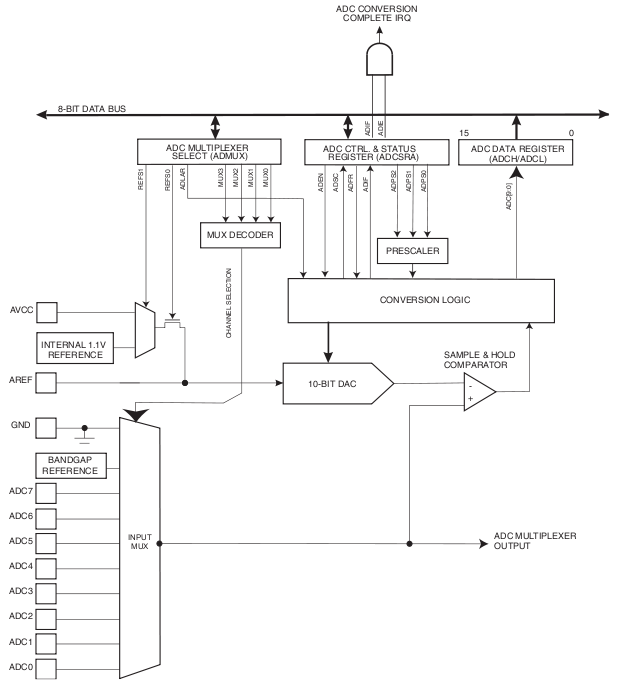

ADCにはサンプル・ホールド回路が搭載されており、変換動作中のADCへの入力電圧が一定値となるように動作します。 ADCのブロック図をFigure23-1(p.244)に示します。

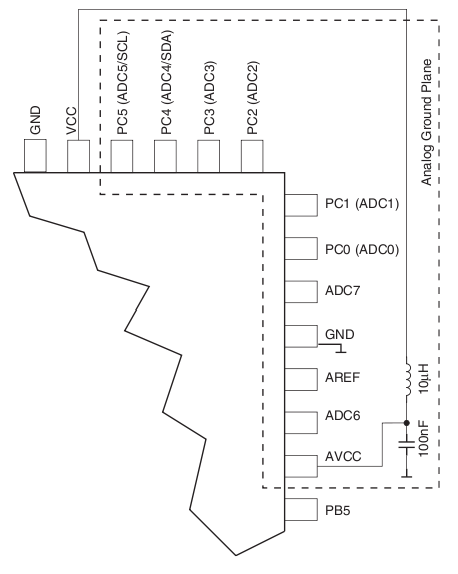

ADCには、専用の電源端子としてAVCCが用意されています。 AVCCは、VCCの電圧に対して± 0.3V以内の範囲でなければなりません。 この端子の接続については、「ADCのノイズ抑制」(p.249)を参照してください。

1.1V出力の内蔵電圧リファレンス、またはAVCCが参照電圧として利用されます。 AREF端子に外付けのデカップリング・コンデンサを接続することで、電圧リファレンスの耐ノイズ特性を改善することができます。

ADCを使用する際には、「消費電力を最小にする」(p.40)に記載されている、ADC電力低減ビットPRADCに0を書き込んで節電機能を無効にしてください。

ADCは、アナログ入力電圧を連続した近似動作によって10ビットのデジタル値に変換します。 変換結果の最小値はGND電圧を表しており、最大値はAREF端子の電圧値から1LSB分差し引いた値を表します。 ADMUXレジスタのREFSnビットを設定することによって、AVCC、あるいは内蔵電圧リファレンスの1.1VをAREF端子に接続することができます。 したがって、AREF端子に外付けのデカップリング・コンデンサを接続して、内蔵電圧リファレンスのノイズ耐性を改善することができます。

Figure 23-1. A/Dコンバータ回路の動作ブロック図

ADMUXレジスタのMUXビットに値を書き込んで、アナログ入力チャンネルを選択できます。 ADC入力端子のいずれか、GND、固定値のバンドギャップ電圧リファレンスのうち一つをADCのシングル・エンド入力とすることができます。 ADCSRAレジスタのADC有効ビット、ADENをセットするとADCが有効になります。 電圧リファレンスと入力チャンネルの選択は、ADENビットがセットされない限り、有効な選択となりません。 ADENビットがクリアされている場合、ADCは電力を消費しません。したがって、消費電力を低くするためにスリープ・モードに入る際には、ADCへの電力供給をオフにしておくことが推奨されます。

ADCの生成する10ビットの変換結果はADCデータ・レジスタ、ADCH、ADCLに出力されます。 デフォルト設定では、変換結果はビットを右側へ詰め込んだ表現形式で保存されます。 ADMUXレジスタのADLARビットをセットすることにより、ビットを左側に詰め込んだ表現形式とすることもできます。

ビットを左側に配置した変換結果を使用する場合、8ビット以上の精度が必要でなければ、ADCHレジスタの値のみを読み取るだけで十分です。 それ以外の場合は、ADCLレジスタを最初に、その次にADCHレジスタを読み取り、二つのデータ・レジスタの内容が同一の変換結果からのものとなるようにしなければなりません。 ADCLレジスタを読み取ると、ADCによるデータ・レジスタへのアクセスが禁止されます。 つまり、ADCLレジスタを読み取ってからADCHレジスタを読み取る前に新たに変換動作が完了した場合、データ・レジスタADCL、ADCHの更新は行われず、その変換結果は失われることになります。 ADCHを読み取ると、ADCによるADCH、ADCLレジスタへのアクセスが再び有効になります。

ADCには、変換完了時に発生させることができる割り込みが備わっています。 ADCHとADCLレジスタの読み取りの間の、ADCがデータ・レジスタへのアクセスを禁止されている期間に変換動作が完了し、変換結果が失われる場合であっても、割り込みは発生します。

「消費電力を最小にする」(p.40)にあるADC電力低減ビット、PRACに0を書きこんで無効にし、ADC変換開始ビット、ADSCに1を書きこむと、一回の変換動作が開始します。ADSCビットは、変換動作が進行中の間Highのままとなり、変換が完了するとハードウェアによりクリアされます。 変換動作中に、入力チャンネルの選択を変更すると、ADCは進行中の変換を完了してから、チャンネルの変更を行います。

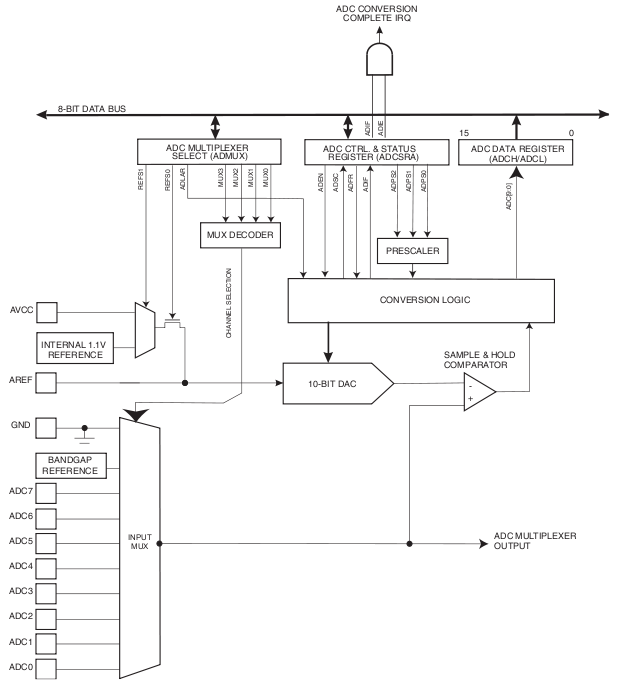

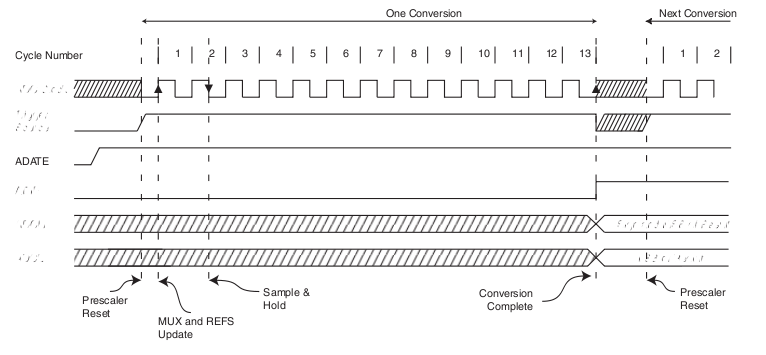

別の方法として、様々な要因をトリガーとして自動的に変換動作をスタートさせることができます。 この自動トリガー動作は、ADCSRAレジスタのADC自動トリガー有効ビット、ADATEをセットすると有効になります。 トリガー要因の選択は、ADCSRBレジスタのADCトリガー選択ビット、ADTS(トリガー要因の一覧については、ADTSビットの説明を参照)によって行います。 選択されたトリガー要因の立ち上がりエッジにより、ADCのプリスケーラがリセットされ、変換動作が開始されます。 この機能により、一定の時間間隔で変換動作を開始することができます。 変換完了時にトリガー要因の信号レベルがHighのままになっている場合、次の変換動作は開始されません。 変換動作中に新たにトリガー要因に立ち上がりエッジが発生した場合、そのエッジは無視されます。 なお、各トリガーに対応する割り込みが無効になっている場合や、SREGのグローバル割り込み有効ビットがクリアされている場合であっても、割り込みフラグはセットされます。 したがって、割り込みを発生させることなく、変換動作をトリガーにより開始することができます。 ただし、割り込みフラグをクリアしないと、次の割り込みイベントによる変換動作を開始することはできません。

Figure 23-2. ADC 自動トリガー回路

ADC割り込みフラグをトリガー要因として使用することにより、変換動作が完了すると即座に次の変換を開始させることができます。 これにより、ADCはフリーラン・モードで動作し、自動的にサンプリングを行って、ADCデータ・レジスタを更新しつづけます。 最初の変換動作は、ADCSRAレジスタのADSCビットに1を書きこんで開始させなければなりません。 このモードでは、ADC割り込みフラグ、ADIFがクリアされているかどうかに関係なく、ADCが連続して変換動作を行います。

自動トリガーを有効にしている場合でも、ADCSRAレジスタのADSCビットに1を書き込むことにより、単一の変換動作を開始させることができます。 ADSCビットは変換動作が進行中かどうかを判定するために使用することもできます。 変換動作の開始要因に関係なく、変換動作中のADSCビットの読み取り値は1となります。

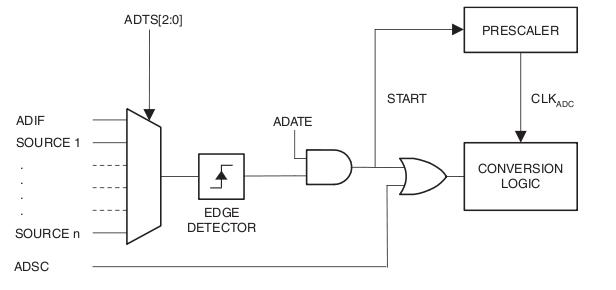

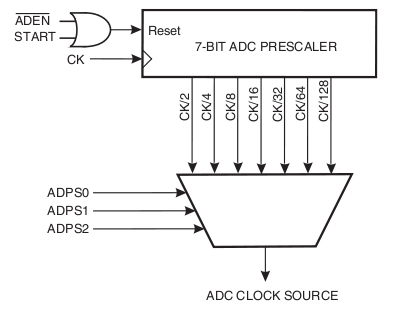

Figure 23-3. ADC プリスケーラ

デフォルト設定では、連続近似変換回路は、最大精度を得る場合50kHzから200kHzのクロック入力を必要とします。 必要な精度が10ビットよりも低い場合、ADCへの入力クロックの周波数を200kHZよりも高く設定して、より高いサンプリング・レートを実現することができます。

ADCモジュールにはプリスケーラが備わっており、100kHzよりも高い周波数のCPUクロックからADCに適切なクロック周波数を生成することができます。 プリスケーラの設定はADCSRAレジスタのADPSビットで行います。

プリスケーラのカウント動作は、ADCSRAレジスタのADENビットをセットしてADCを有効にした時から始まります。 ADENビットがセットされている間、プリスケーラはカウント動作を継続し、ADENビットがLowになった場合、ゼロ固定となります。

ADCSRAレジスタのADSCビットをセットして単一の変換動作を開始する場合、その変換動作はADCクロックサイクルの次の立ち上がりエッジにより開始されます。

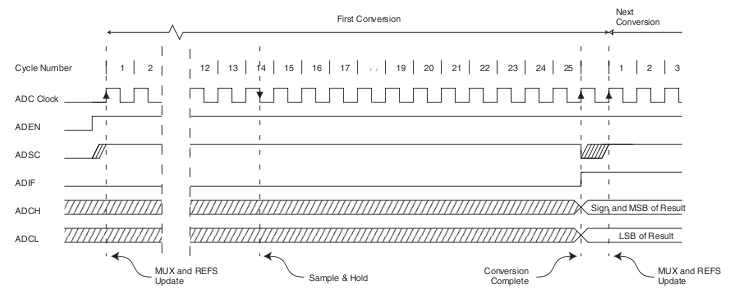

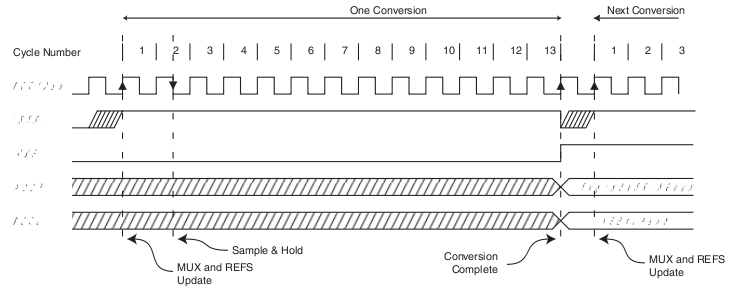

通常の変換動作には、ADCクロック13サイクルの時間がかかります。 ADCを有効(ADCSRAレジスタのADENビットをセット)にした最初の変換動作には、アナログ回路を初期化するため、 25サイクルが必要です。

バンドギャップ電圧リファレンスがADCの入力として使用されている場合、その電圧が安定するまでに一定の時間が必要です。 安定していない状態で変換を行うと、最初に読み取る変換結果は正確な値とならない場合があります。

通常の変換動作を開始後1.5ADCサイクル、および、最初の変換動作開始から13.5ADCサイクル後に、サンプル・ホールド動作が行われます。 変換動作が完了すると、変換結果がADCデータ・レジスタに書きこまれ、ADIFビットがセットされます。 単一変換モードでは、同時にADSCビットがクリアされます。 その後、ソフトウェアによりADSCビットを再度セットすると、その後の最初のADCクロックの立ち上がりエッジで次の変換動作が開始されます。

自動トリガー・モードでは、トリガー要因が発生したときにプリスケーラがリセットされます。 これにより、トリガー要因から変換開始までの遅延時間を一定にすることができます。 このモードでは、トリガー要因の立ち上がりエッジから、2ADCクロック後のにサンプル・ホールド回路が動作します。 同期回路の動作に3CPUサイクルを消費します。

フリーラン・モードでは、ADSCビットがHighになっている間、変換動作が完了すると即座に次の変換が開始されます。 変換動作のタイミングをTable 23-1(p.248)にまとめます。

Figure 23-4. ADCタイミング・チャート

最初の変換動作(単一変換モード)

Figure 23-5. ADCタイミング・チャート

単一変換モード

Figure 23-6. ADCタイミング・チャート、自動トリガー・モード

Figure 23-7. ADCタイミング・チャート、フリーラン・モード

| 条件 | サンプル&ホールド時間(変換開始からのサイクル数) | 変換時間(サイクル数) |

|---|---|---|

| 最初の変換 | 13.5 | 25 |

| 通常の変換 | 1.5 | 13 |

| 自動トリガーによる変換 | 2 | 13.5 |

ADMUXレジスタのMUXnビット、およびREFS1:0ビットは、CPUからランダム・アクセスできる一時レジスタを介してシングル・バッファ接続されています。 このしくみにより、A/D変換動作中の安全な時間帯でのみ、チャンネルやリファレンス電圧の選択動作が行われます。 変換動作が開始するまでは、チャンネルやリファレンス電圧の選択は、変更があると、それに応じていつでも更新されます。 いったん変換動作が開始すると、チャンネルやリファレンス電圧の選択はロックされ、A/Dコンバータに必要なサンプリング時間を確保します。 A/D変換完了(ADCSRAレジスタのADIFフラグがセットされるとき)の直前の最終ADCクロックにおいて、チャンネルやリファレンス電圧選択の更新動作が再開されます。 なお、ADSCレジスタに書き込みを行った次のADCクロックの立ち上がりで、変換動作が開始することにご注意ください。 したがって、ユーザープログラム中では、ADSCレジスタへの書込み後、ADCクロック1サイクル経過するまでの時間帯に、チャンネル選択やリファレンス電圧選択を変更するような値をADMUXレジスタに書きこむべきではありません。

自動トリガー・モードを使用している場合は、トリガー・イベントが発生する正確な時間が予測不能な場合があります。 ADMUXレジスタの更新を行う場合は、設定変更によって変換動作が受ける影響を最小限にするために特別な配慮が必要となります。

ADATEビットとADENビットの両方に1をセットしている場合、割り込みイベントがいつ発生するかを予測することは原理的に不可能です。 ADMUXレジスタをこの状態で変更した場合、その次の変換動作がADMUXの変更前、変更後いずれの設定によるものかをユーザーが知るすべはありません。ADMUXレジスタの変更を安全に行うために、以下のような条件で実行してください。

ADMUXレジスタの更新を以上の条件のもとで行った場合、新しい設定値が次回のA/D変換動作に反映されます。

チャンネルの選択を変更する際は、ユーザーは下記の原則に注意して正しいチャンネルが選択されるようにしなければなりません。

単一変換モードでは、必ず変換動作を開始する前にチャンネル選択をしてください。 ADSCビットに1を書き込んだ後、ADCクロック1サイクル経過後でもチャンネル選択の変更をすることができますが、最も簡単な方法は、変換動作が完了するのを待ち、その後、チャンネル選択の変更をすることです。

フリーラン・モードでは、必ず最初の変換動作を始める前にチャンネル選択をしてください。 ADSCビットに1を書き込んだ後、ADCクロック1サイクル経過後にチャンネル選択の変更をすることができますが、最も簡単な方法は、最初の変換動作が完了するのを待ち、その後、チャンネル選択の変更をすることです。このとき、次の変換動作が自動的に開始されているので、次回の変換結果は変更前のチャンネルを反映したものになります。それ以降の変換動作では、新しく選択したチャンネルが反映されます。

A/D変換の電圧リファレンス(VREF)は、A/D変換の対象となる電圧の上限を示しています。シングル・エンドのチャンネルにおけるVREFを超える入力は全て同一の値0x3FFに変換されます。VREFには、AVCC、内蔵の1.1V電圧リファレンス、または、外部入力端子AREFのいずれかを選択できます。

AVCCはパッシブ・スイッチを通してADCに接続されています。 内蔵1.1V電圧リファレンスは、内蔵のバンドギャップ電圧リファレンスから内蔵アンプを通して生成されています。 どの場合でも、AREF端子はADCに直接接続されており、AREF端子とグラウンドの間にコンデンサを接続することで、電圧リファレンスのノイズ耐性を高めることができます。 VREFの電圧はAREF端子に高インピーダンスの電圧計を接続して測定することもできます。 VREFは高インピーダンスの電圧源なので、回路全体としてVREFに容量性負荷以外のものを接続するべきではありません。

ユーザーがAREF端子に固定値の外部電圧源を接続する場合、内部電圧リファレンスとの短絡を防止するため、そのアプリケーションで他の電圧リファレンスのオプションを選択してはいけません。 外部からの電圧がAREF端子に供給されていない場合に限り、AVCCや1.1Vを選択肢として切り替え使用することができます。 電圧リファレンスを切り替えた場合、その後の最初のAD変換動作の結果は不正確な場合があるので、ユーザーは最初の変換結果を破棄することが推奨されます。

ADCにはスリープ・モード中に変換を行い、CPUコアや他の周辺I/Oから発生するノイズを低減するノイズ抑制機能が備わっています。ノイズ抑制機能はADCノイズ低減モードとアイドル・モードで使用できます。 この機能の使用は、下記の手順でおこないます。

アイドル・モード、ADCノイズ低減モード以外のスリープ・モードに入る場合、ADCは自動的にオフにならないことにご注意ください。その他のスリープモードに入る場合、ADENビットにゼロを書き込み、余計な電力を消費しないようにすることが推奨されます。

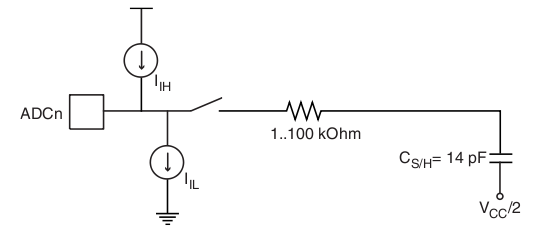

シングル・エンド・チャンネルのアナログ入力回路をFigure23-8に示します。 ADCn端子に供給されるアナログ電圧源には、ADCの入力チャンネルが選択されているかどうかに関係なく、端子の容量成分と漏れ電流の影響を受けます。 (訳注:Figure23-8には「端子の容量成分」は記載がありません。本文記述によれば、I_ILと並列に接続される容量成分と思われます) チャンネルが選択されている場合は、電圧源は、直列抵抗(入力経路の抵抗成分の合成値)を通して、サンプル・ホールド回路のコンデンサを駆動しなければなりません。

ADCは、出力インピーダンスが約10kω以下のアナログ信号を入力として受けるように最適化されています。 その要件を満たした電圧源を使用する場合はサンプリング時間は無視できるほど小さくなります。 より高い出力インピーダンスをもつ電圧源を使用する場合、サンプリング時間の長さはサンプル・ホールド回路のコンデンサの充電時間に依存し、この時間は広範囲にわたって変化します。 サンプル・ホールド回路のコンデンサの充電時間を最小限にするため、出力インピーダンスが低く、信号の変化がゆっくりとしている電圧源の使用が推奨されます。

予測不可能な信号の重畳による歪みを防止するため、ナイキスト周波数(fADC/2)よりも高い信号成分が、どのチャンネルにも現れないようにする必要があります。 ADCに信号が入力される前に、ロー・パス・フィルタによって高い周波数成分を取り除いておくことが推奨されます。

Figure 23-8. アナログ入力回路

デバイス内部、および外部のデジタル回路が発生するEMIにより、アナログ電圧の測定精度が悪化する場合があります。 A/D変換の精度が最重要項目である場合には、下記のような手段によりノイズレベルを低減することができます。

Figure 23-9. ADCへの電源接続

nビットのシングル・エンドA/Dコンバータは、GNDとVREF間の電圧を2n段階(x LSB)に直線的に変換します。 もっとも小さなコードは0となり、最も大きなコードは2n-1となります。

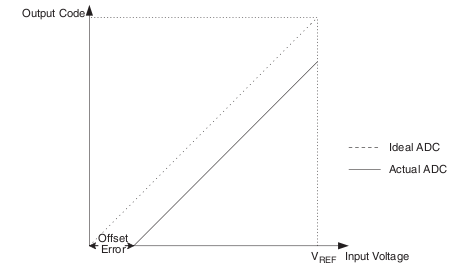

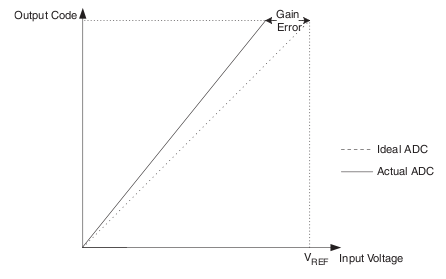

理想的な動作との相違点は、いくつかのパラメータにより表現されます。

Figure 23-10. オフセット誤差

Figure 23-11. ゲイン誤差

Figure 23-12. 積分非直線性 (INL)

Figure 23-13. 微分非直線性 (DNL)

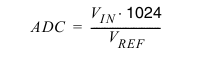

変換が完了する(ADIFフラグがHighになる)と、変換結果がADC変換出力レジスタ(ADCL、ADCH)に表れます。

シングル・エンドの変換における変換結果は

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x7C) | REFS1 | REFS0 | ADLAR | - | MUX3 | MUX2 | MUX1 | MUX0 | ADMUX |

| Read/Write | R/W | R/W | R/W | R | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

これらのビットにより、Table 23-2に示すように、電圧リファレンスを選択します。 変換動作中にこれらのビットを変更した場合、変換が完了する(ADCSRAレジスタのADIFビットがセット)まで、その変更は有効になりません。 内蔵電圧リファレンスを使用する設定は、AREF端子に外部の電圧リファレンスが接続されている場合には使用してはいけません。

Table 23-2. A/D変換用電圧リファレンスの選択

| REFS1 | REFS0 | 電圧リファレンスの選択 |

|---|---|---|

| 0 | 0 | AREF端子の電圧を使用。 内蔵電圧リファレンスはオフ。 |

| 0 | 1 | AVCCを使用。 AREF端子には外部コンデンサを接続すること。 |

| 1 | 0 | (予約) |

| 1 | 1 | 内蔵1.1V電圧リファレンス。 AREF端子には外部コンデンサを接続すること。 |

ADLARビットにより、ADCデータ・レジスタでのAD変換結果のビット表現方法が変わります。

ADLARビットに1を書き込むと、変換結果が左詰めで表現されます。 0を書きこむと、変換結果が右詰めで表現されます。 ADLARビットを変更すると、現在進行中の変換動作に関係なく、ADCデータ・レジスタの内容が即座に変化します。 このビットの詳細については、「ADCL、およびADCH – ADCデータ・レジスタ」(p.257)を参照してください。

このビットはATmega48/88/168では予約ビットとなっており、読み取り時には常にゼロとなります。

これらのビット値により、どのアナログ入力をADCに接続するかを選択します。 詳細は、Table 23-3を参照してください。 これらのビットを変換動作中に変更した場合、変換が完了する(ADCSRAレジスタのADIFビットがセット)まで、その変更は有効になりません。

Table 23-3.

入力チャンネルの選択

| MUX3..0 | シングル・エンド入力 |

|---|---|

| 0000 | ADC0 |

| 0001 | ADC1 |

| 0010 | ADC2 |

| 0011 | ADC3 |

| 0100 | ADC4 |

| 0101 | ADC5 |

| 0110 | ADC6 |

| 0111 | ADC7 |

| 1000 | (予約) |

| 1001 | (予約) |

| 1010 | (予約) |

| 1011 | (予約) |

| 1100 | (予約) |

| 1101 | (予約) |

| 1110 | 1.1V (V_BG, 内蔵電圧リファレンス) |

| 1111 | 0V (GND) |

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x7A) | ADEN | ADSC | ADATE | ADIF | ADIE | ADPS2 | ADPS1 | ADPS0 | ADCSRA |

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

このビットに1を書きこむとADCが有効になります。 ゼロを書きこむと、ADCはオフとなります。 変換動作進行中にADCをオフにすると、その変換動作は中断されます。

単一変換モードで、このビットに1を書きこむと、変換動作を開始します。 フリーラン・モードで、このビットに1を書きこむと、最初の変換動作を開始します。 ADCを有効にして、ADSCビットへの書き込みを行ってから、あるいは、ADCを有効にすると同時にADSCへの書き込みを行なってから、最初の変換が開始するまでには、通常のADCクロック13サイクルではなく、25サイクル分の時間がかかります。最初の変換動作では、ADCの初期化が行われます。

変換動作が進行中の間、ADSCはリード時に1となります。変換が完了すると、0に戻ります。 このビットに0を書きこんでも、動作に変化は発生しません。

このビットに1を書きこむと、ADCの自動トリガー機能が有効になります。 選択されたトリガー信号の立ち上がりエッジによりADCが変換を開始します。 トリガー要因はADCトリガー選択ビット(ADCSRBレジスタのADTSビット)により選択します。

ADCの変換が完了し、データ・レジスタが更新されると、このビットがセットされます。 ADIEビット、およびSREGのIビットがセットされていれば、ADC変換完了割り込みが実行されます。

対応する割り込みベクトルが実行されると、ADIFビットはハードウェアによりクリアされます。 別の方法として、ADIFに1を書き込むことによりクリアすることができます。 ADCSRAレジスタに対して、リード・モディファイ・ライトを行うと、待機中になっている割り込みを無効にしてしまう場合があります。 これは、SBI、CBI命令を使用する場合にも当てはまります。 (訳注:たとえば、変換を開始するためにADSCビット(第6ビット)に1を書きこもうとして、「ADCSRAをリード」し、その値の「第6ビットを1にセット」し、「ADCSRAに書き戻す」という一連の動作において、ADIFビット(第4ビット)がセットされていた場合、同ビットをクリアしてしまうということ)

このビットに1を書き込み、SREBのIビットがセットされていれば、ADC変換完了割り込みが有効になります。

これらのビットにより、システム・クロック周波数からADCへのクロックを生成する分周比を決定します。

Table 23-4. ADCプリスケーラ選択

| ADPS2 | ADPS1 | ADPS0 | 分周比 |

|---|---|---|---|

| 0 | 0 | 0 | 2 |

| 0 | 0 | 1 | 2 |

| 0 | 1 | 0 | 4 |

| 0 | 1 | 1 | 8 |

| 1 | 0 | 0 | 16 |

| 1 | 0 | 1 | 32 |

| 1 | 1 | 0 | 64 |

| 1 | 1 | 1 | 128 |

| ビット | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | |

| (0x79) | - | - | - | - | - | - | ADC9 | ADC8 | ADCH |

| (0x78) | ADC7 | ADC6 | ADC5 | ADC4 | ADC3 | ADC2 | ADC1 | ADC0 | ADCL |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | ||

| Read/Write | R | R | R | R | R | R | R | R | |

| R | R | R | R | R | R | R | R | ||

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| ビット | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | |

| (0x79) | ADC9 | ADC8 | ADC7 | ADC6 | ADC5 | ADC4 | ADC3 | ADC2 | ADCH |

| (0x78) | ADC1 | ADC0 | - | - | - | - | - | - | ADCL |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | ||

| Read/Write | R | R | R | R | R | R | R | R | |

| R | R | R | R | R | R | R | R | ||

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

ADCの変換が完了すると、変換結果がこの二つのレジスタに表れます。

ADCLレジスタを読みだした後、ADCHレジスタを読み出すまで、ADCデータ・レジスタの内容は更新されません。 したがって、変換結果を左詰めで表現しており、8ビット以上の精度を必要としない場合、ADCHレジスタのみを読み出すことで十分となります。 その他の場合は、ADCLレジスタを最初に読み出し、その後ADCHレジスタを読み出します。

ADMUXレジスタのADLARビットの値により、このレジスタから読み出す方法が変わります。 ADLARビットがセットされている場合、変換結果は左詰めで表現されます。ADLARビットがクリア(デフォルト値)されている場合、変換結果は右詰めで表現されます。

これらのビットにより、変換結果を表現しています。詳細は「ADC変換結果」(p.254)に記載されています。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x7B) | - | ACME | - | - | - | ADTS2 | ADTS1 | ADTS0 | ADCSRB |

| Read/Write | R | R/W | R | R | R | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

これらのビットは将来拡張のために予約となっています。 将来のデバイスとの互換性を確保するため、ADCSRBレジスタに書き込みする場合、これらのビットには常に0にしてください。

ADCSRAレジスタのADATEビットに1がセットされている場合、これらのビットによりADC変換のトリガー要因を選択します。 ADATEビットがクリアされている場合、ADTS2:0ビットの設定内容は、ADCの動作に影響ありません。 変換動作は選択された割り込みフラグの立ち上がりエッジによりトリガーされます。 クリア状態のトリガー要因から、セット状態のトリガー要因に設定変更を切り換えることにより、トリガー要因の立ち上がりエッジが生成されることに注意してください。 ADCSRAレジスタのADENビットがセットされている場合、このトリガー要因の立ち上がりにより変換動作が始まります。 フリーラン・モード(ADTS[2:0]=0)へと切り換える場合は、ADC割り込みフラグがセットされている場合であっても、トリガー・イベントは生じません。

Table 23-5.

ADC自動トリガー要因の選択

| ADTS2 | ADTS1 | ADTS0 | トリガー要因 |

|---|---|---|---|

| 0 | 0 | 0 | フリーラン・モード |

| 0 | 0 | 1 | アナログ・コンパレータ |

| 0 | 1 | 0 | 外部割込みリクエスト0 |

| 0 | 1 | 1 | タイマー/カウンター0 比較一致A |

| 1 | 0 | 0 | タイマー/カウンター0 オーバーフロー |

| 1 | 0 | 1 | タイマー/カウンター1 比較一致B |

| 1 | 1 | 0 | タイマー/カウンター1 オーバーフロー |

| 1 | 1 | 1 | タイマー/カウンター1 キャプチャ・イベント |

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x7E) | - | - | ADC5D | ADC4D | ADC3D | ADC2D | ADC1D | ADC0D | DIDR0 |

| Read/Write | R | R | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

これらのビットは将来拡張のための予約となっています。 将来のデバイスとの互換性を保持するため、DIDR0レジスタに書き込みする場合、これらのビットは常に0にしてください。

このビットに1を書き込むと、ADC各端子に対応するデジタル入力バッファが無効になります。それぞれの端子に対応するポートのPINレジスタのビットは常に0になります。 ADC5..0端子にアナログ信号を入力していて、その端子をデジタル入力として使用しない場合は、このビットに1を書き込みデジタル入力バッファでの消費電力が少なくなるようにしてください。

なお、ADC7およびADC6のADC端子にはデジタル入力バッファが接続されていないので、デジタル入力無効化ビットは必要ありません。