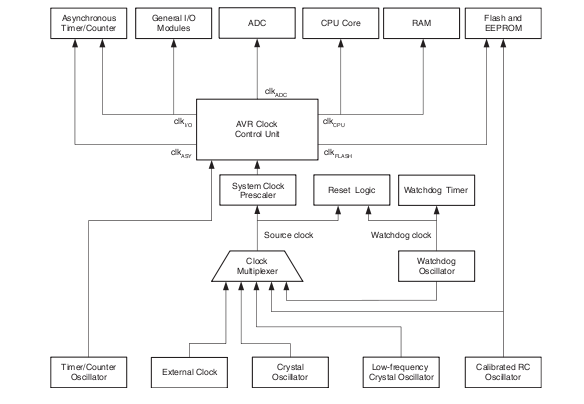

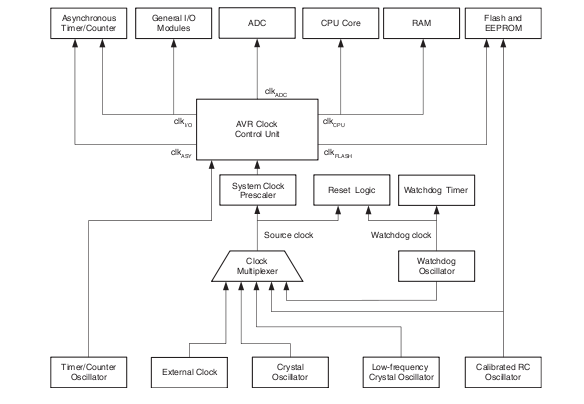

Figure 8-1 にAVRのメイン・クロック・システムとその配分の様子を示します。図に示された全てのクロックが常に有効になっているとは限りません。消費電力を小さくするため、使用されないモジュールへのクロックを、「パワー・マネージメントとスリープ・モード」(p.38)にあるように、各種のスリープモードを用いて停止させることができます。各クロック・システムの詳細は下記の通りです。

Figure 8-1. クロックの配分

CPUクロックはAVRコアの動作に関係するシステムの各部に配線されています。関係するモジュールの例は、汎用レジスタ・ファイル、ステータス・レジスタ、スタック・ポインタを保持しているデータメモリなどです。CPUクロックを停止すると、一般的な命令の実行や演算がCPUコアで行われなくなります。

I/Oクロックは、タイマー/カウンター、SPI、USARTといった大半のI/Oモジュールで使用されています。I/Oクロックは外部割込みモジュールにも使われていますが、外部割込みの一部には非同期ロジックにより監視されているものもあり、その場合、I/Oクロックが停止している状態でも割込みを検知することが可能です。また、USIモジュールでのスタート・コンディションの検出は、clkI/Oが停止していても非同期で実行され、2線式インターフェース(TWI)のアドレス認識による割込みは、すべてのスリープモードで動作します。

(訳注:最後の文は原文の省略がはげしいので、言葉を補った。9章 「パワーマネージメントとスリープモード」の 9.1, 9.4、および 21章 「2線式インターフェース(TWI)」の 21.5.3, 21.5.4 を参照のこと)

フラッシュ・クロックはフラッシュ・メモリのインターフェースの動作を制御します。フラッシュ・クロックは通常CPUクロックが有効であるとき、同時に有効になっています。

非同期タイマー・クロックにより、外部クロックまたは外部に接続された32kHzのクリスタルによるクロックで、非同期タイマー/カウンターが直接動作することが可能になっています。この専用クロック供給回路により、デバイスがスリープモードにある状態であっても、タイマー/カウンターをリアルタイム・クロックとして使用することが可能になります。

A/Dコンバーターは専用のクロック供給回路を持っています。この構造により、CPUクロックとI/Oクロックの両方を、デジタル回路のノイズを低減するために停止させることが可能です。これによって、より正確なA/D変換結果を出すことができます。

デバイスには、下記のクロック供給オプションがあり、それぞれ示されているとおり、フラッシュメモリのヒューズ・ビットにより選択可能です。選択されたクロック供給源からのクロックは、AVRのクロック発生回路へのクロック入力となり、適切なモジュールへと配分されます。

| デバイスのクロック供給オプション | CKSEL3..0 |

|---|---|

| 低消費電力クリスタル発振器 | 1111 - 1000 |

| 最大振幅のクリスタル発振器 | 0111 - 0110 |

| 低周波数クリスタル発振器 | 0101 - 0100 |

| 内蔵 128kHz RC発振器 | 0011 |

| 調整済み内蔵 RC発振器 | 0010 |

| 外部クロック | 0000 |

| (予約) | 0001 |

注意:

デバイスは内蔵RC発振器を8MHzに設定し、CKDIV8ヒューズビットがプログラムされた状態で出荷されており、システム・クロックは1.0MHzとなっています。スタートアップ・タイムは最大値に設定され、タイム・アウト期間が有効になっています。(CKSEL = "0010", SUT = "10", CKDIV8 = "0")

出荷時設定により、すべてのユーザーは、どのプログラミング・インターフェースを用いても、クロック供給源の設定を、希望の設定に確実に変更できるようになっています。

どのクロック供給源においても、発振を開始するためには、VCC電圧が十分に高くなっている必要があり、また、十分に安定した発振を行うまでに最低限必要な最小クロック数があります。

十分なVCC電圧が供給されるように、デバイスは内部リセット信号を発効し、その信号には、デバイスのリセット入力が他のすべてのリセット信号供給源から解放された時点からのタイムアウト遅延時間(tTOUT)を設定しています。「システムのコントロールとリセット」(p.44)に、内部リセットが開始される条件について記載されています。遅延時間(tTOUT)は、ウォッチドッグ発振器により駆動され、遅延時間のクロック数はSUTxとCKSELxヒューズビットによって設定されます。Table 8-2に選択可能な遅延時間を示します。ウォッチドッグ発振器の周波数は、「代表特性」(p.314)に示されているとおり、供給電圧に依存します。

| タイム・アウト(typ) (VCC = 5.0V) |

タイム・アウト(typ) (VCC = 3.0V) |

クロック数 |

|---|---|---|

| 0 ms | 0 ms | 0 |

| 4.1 ms | 4.3 ms | 4K (4,096) |

| 65 ms | 69 ms | 8K (8,192) |

必要とされる最小電圧がVCCに供給されるまでの間AVRをリセット状態で保持するのが、遅延時間の主な目的です。この遅延においては、実際の電圧を監視しているわけではなく、VCCの立ち上がり時間よりも長い遅延時間を選択する必要があります。それができない場合には、内蔵または外部のブラウン・アウト検出回路を使用してください。BOD回路によって、リセット状態が解放されるまでに十分なVCC電圧を供給することができ、タイム・アウト遅延時間を無効に設定することができます。ブラウン・アウト検出回路を使わないで、タイム・アウト遅延時間を無効にする設定は推奨されません。

発振器には、クロックが十分に安定するまでに必要な最小限の発振クロック数があります。内臓のリップル・カウンターが発振器の出力するクロックを監視し、設定されたクロック数の期間、内蔵リセット信号を有効に保持します。その後、リセット状態が解放され、デバイスが動作実行を開始します。発振器の推奨スタートアップ時間は、外部クロックでは6サイクル、低周波数クリスタル発振回路では32kサイクルと、クロックの種類によって異なっています。

クロックのスタートアップ・シーケンスには、デバイスがリセット状態から実行開始するまで、タイム・アウト遅延時間とスタートアップ時間の両方が含まれます。パワーセーブ・モード、または、パワーダウン・モードからスタートアップする場合、VCCは十分に高い電圧になっているという前提で、スタートアップ時間のみが含まれます。

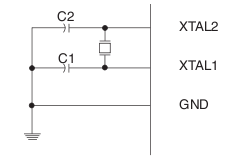

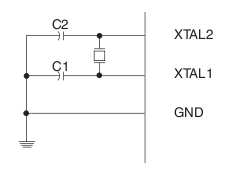

XTAL1およびXTAL2端子はそれぞれ、Figure8-2にあるように、内蔵発振器として使用できる反転増幅器の入力と出力です。水晶発振子もセラミック発振子も使用可能です。

クリスタル発振器は、XTAL2出力の振幅電圧を低く抑えた低消費電力発振器です。もっとも少ない電力消費ですが、他のクロック入力をドライブする能力はなく、ノイズの多い環境下では影響をより受けやすい可能性があります。そのような条件での動作には、「フルスイング出力クリスタル発振器」を参照してください。

C1とC2は、水晶発振子でもセラミック発振子でも、同じ値である必要があります。両コンデンサの最適値は、使用されている水晶発振子やセラミック発振子、寄生容量、そして使用環境の電磁気ノイズに依存します。Table 8-3に、クリスタル発振子を使用する際のコンデンサの選択について最初に考察すべきガイドラインを記します。セラミック発振子については、製造メーカーによって指定されている値を使用してください。

低消費電力発振器は、三つの異なる動作モードがあり、それぞれ特定の周波数範囲において最適設計されています。各動作モードは、Table 8-3 (p.29)にあるとおり、CKSEL3..1ヒューズ・ビットにより選択されます。

| 周波数の範囲(MHz) | コンデンサC1,C2の推奨範囲(pF) | CKSEL3..1 |

|---|---|---|

| 0.4 - 0.9 | - | 100 (2) |

| 0.9 - 3.0 | 12 - 22 | 101 |

| 3.0 - 8.0 | 12 - 22 | 110 |

| 8.0 - 16.0 | 12 - 22 | 111 |

注意

CKSEL0ヒューズ・ビットをSUT1..0ヒューズ・ビットとともに使用することで、Table 8-4にあるようにスタート・アップ時間を選択できます。

| 発振子/供給電圧の条件 | パワーダウン・モードおよびパワーセーブ・モードからのスタートアップ時間 | リセット後の追加遅延時間(Vcc = 5.0V) | CKSEL0 | SUT1..0 |

|---|---|---|---|---|

| セラミック発振子、立ち上がりの速い電源 | 258 CK | 14CK + 4.1ms (1) | 0 | 00 |

| セラミック発振子、立ち上がりの遅い電源 | 258 CK | 14CK + 65ms (1) | 0 | 01 |

| セラミック発振子、BOD有効 | 1K CK | 14CK (2) | 0 | 10 |

| セラミック発振子、立ち上がりの速い電源 | 1K CK | 14CK + 4.1ms (2) | 0 | 11 |

| セラミック発振子、立ち上がりの遅い電源 | 1K CK | 14CK + 65ms (2) | 1 | 00 |

| クリスタル発振子、BOD有効 | 16K CK | 14CK | 1 | 01 |

| クリスタル発振子、立ち上がりの速い電源 | 16K CK | 14CK + 4.1ms | 1 | 10 |

| クリスタル発振子、立ち上がりの遅い電源 | 16K CK | 14CK + 65ms (2) | 1 | 11 |

注意

XTAL1およびXTAL2端子はそれぞれ、Figure8-2にあるように、内蔵発振器として使用できる反転増幅器の入力と出力です。水晶発振子もセラミック発振子も使用可能です。

このクリスタル発振器は、XTAL2にrail-to-railの振幅の出力を行うフルスイング出力の発振器です。他のクロック入力をドライブしたり、ノイズの多い環境下で使用する用途に向いています。消費電流は「低消費電力クリスタル発振器」(p.28)よりも大きくなります。フルスイング出力クリスタル発振器は、VCC = 2.7〜5.5Vの範囲でのみ動作することにご注意ください。

C1とC2は、水晶発振子でもセラミック発振子でも、同じ値である必要があります。両コンデンサの最適値は、使用されている水晶発振子やセラミック発振子、寄生容量、そして使用環境の電磁気ノイズに依存します。Table 8-6に、クリスタル発振子を使用する際のコンデンサの選択について最初に考察すべきガイドラインを記します。セラミック発振子については、製造メーカーによって指定されている値を使用してください。

動作モードはTable 8-5にあるように、CKSEL3..1ヒューズ・ビットによって選択できます。

| 周波数の範囲(MHz) | コンデンサC1,C2の推奨範囲(pF) | CKSEL3..1 |

|---|---|---|

| 0.4 - 20 | 12 - 22 | 011 |

注意

|

発振子/ 供給電圧の条件 |

パワーダウンおよびパワーセーブからのスタート・アップ時間 | リセットからの追加遅延時間 (Vcc = 5.0V) | CKSEL0 | SUT1..0 |

|---|---|---|---|---|

| セラミック発振子、立ち上がりの速い電源電圧 | 258 CK | 14CK + 4.1 ms (1) | 0 | 00 |

| セラミック発振子、立ち上がりの遅い電源電圧 | 258 CK | 14 CK + 65 ms (1) | 0 | 01 |

| セラミック発振子、BOD有効 | 1K CK | 14 CK (2) | 0 | 10 |

| セラミック発振子、立ち上がりの速い電源電圧 | 1K CK | 14 CK + 4.1 ms (2) | 0 | 11 |

| セラミック発振子、立ち上がりの遅い電源電圧 | 1K CK | 14 CK + 65 ms (2) | 1 | 00 |

| クリスタル発振子、BOD有効 | 16K CK | 14 CK | 1 | 01 |

| クリスタル発振子、立ち上がりの速い電源電圧 | 16K CK | 14 CK + 4.1 ms | 1 | 10 |

| クリスタル発振子、立ち上がりの遅い電源電圧 | 16K CK | 14 CK + 65 ms | 1 | 11 |

注意

専用の低周波数クリスタル発振器をしようすることで、32.768kHzの時計用クリスタルをデバイスのクロック源として使用することができます。このクリスタルは、Figure 8-2に示されたように接続してください。この発振器が選択されている場合、スタート・アップ時間はTable 8-7にあるようにSUTヒューズ・ビットとCKSEL0により決定されます。

| 供給電圧の条件 | パワーダウン・モードおよびパワーセーブ・モードからのスタートアップ時間 | リセット後の追加遅延時間(Vcc = 5.0V) | CKSEL0 | SUT1..0 |

|---|---|---|---|---|

| BOD有効 | 1K CK | 14CK (1) | 0 | 00 |

| 立ち上がりの速い電源 | 1K CK | 14CK + 4.1ms (1) | 0 | 01 |

| 立ち上がりの遅い電源 | 1K CK | 14CK + 65ms (1) | 0 | 10 |

| (予約) | 0 | 11 | ||

| BOD有効 | 32K CK | 14CK | 1 | 00 |

| 立ち上がりの速い電源 | 32K CK | 14CK + 4.1ms | 1 | 01 |

| 立ち上がりの遅い電源 | 32K CK | 14CK + 65ms | 1 | 10 |

| (予約) | 1 | 11 | ||

注意

出荷時の設定として、内蔵のRC発振器が、およそ8.0MHzのクロックを供給するようになっています。供給電圧と温度に依存しますが、このクロックはユーザーによって非常に正確に調整することが可能です。デバイスはCKDIV8ヒューズ・ビットがプログラムされた状態で出荷されます。詳細については、「システム・クロックのプリスケーラ」(p.35)をご覧ください。

このクロックは、Table 8-8に示されたようにCKSELヒューズ・ビットをプログラムすることで選択されます。選択時には、外部追加部品なしで動作します。リセット状態において、ハードウェアがあらかじめプログラムされている調整値をOSCCALレジスタに読み込み、それによってRC発振器が自動的に調整されます。この調整値の精度については、Table 28-1 (p.305)に工場設定の調整値として示されています。

OSCCALレジスタをソフトウェアによって変更することで、「OSCCAL - 発振器調整レジスタ」(p.36)にあるように、工場設定の調整よりも精度の高い調整を行うことが可能です。この調整値の精度については、Table 28-1 (p.305)にユーザー設定の調整値として示されています。

この発振器をデバイスのクロックとして使用する場合でも、ウォッチドッグ発振器はウォッチドッグ・タイマーとリセット時のタイムアウトのクロックとして使用されます。あらかじめプログラムされている調整値についての詳細は、「調整用(キャリブレーション)バイト」(p.287)の節をご覧ください。

| 周波数範囲(MHz) | CKSEL3.0 |

|---|---|

| 7.3 〜 8.1 | 0010 |

注意

| 供給電源の条件 | パワーダウン・モードおよびパワーセーブ・モードからのスタータップ時間 | リセット後に追加される遅延時間(VCC = 5.0V) | SUT1..0 |

|---|---|---|---|

| BOD有効 | 6 CK | 14CK (1) | 00 |

| 立ち上がりの速い電源 | 6 CK | 14CK + 4.1 ms | 01 |

| 立ち上がりの遅い電源 | 6 CK | 14CK + 65 ms (2) | 10 |

| (予約) | 11 | ||

注意

128kHzの内蔵発振器は128kHzのクロックを供給できる低消費電力発振器です。その周波数は、3V, 25℃を標準状態として設定されています。このクロックは、Table 8-10にあるようにCKSELヒューズ・ビットを"11"にプログラムすることにより、システム・クロックとして選択することができます。

| 標準設定周波数 | CKSEL3..0 |

|---|---|

| 128 kHz | 0011 |

注意

このクロック源を選択した場合、スタートアップ時間はTable 8-11にあるとおり、SUTヒューズ・ビットによって決定されます。

(予約) 11

| 供給電源の条件 | パワーダウン・モードおよびパワーセーブ・モードからのスタータップ時間 | リセット後に追加される遅延時間(VCC = 5.0V) | SUT1..0 |

|---|---|---|---|

| BOD有効 | 6 CK | 14CK (1) | 00 |

| 立ち上がりの速い電源 | 6 CK | 14CK + 4.1 ms | 01 |

| 立ち上がりの遅い電源 | 6 CK | 14CK + 64 ms | 10 |

| (予約) | 11 | ||

注意

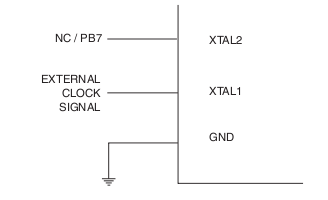

デバイスを外部のクロック源により駆動する場合、XTAL1端子をFigure 8-4 (p.34)にあるように駆動してください。デバイスを外部クロックにより動作させるには、CKSELヒューズ・ビットを"0000"にプログラムしなければなりません(Table 8-12を参照)。

| 周波数 | CKSEL3..0 |

|---|---|

| 0 〜 20 MHz | 0000 |

このクロック源を選択した場合、スタートアップ時間はTable 8-13にあるとおり、SUTヒューズ・ビットによって決定されます。

| 供給電源の条件 | パワーダウン・モードおよびパワーセーブ・モードからのスタータップ時間 | リセット後に追加される遅延時間(VCC = 5.0V) | SUT1..0 |

|---|---|---|---|

| BOD有効 | 6 CK | 14CK | 00 |

| 立ち上がりの速い電源 | 6 CK | 14CK + 4.1 ms | 01 |

| 立ち上がりの遅い電源 | 6 CK | 14CK + 65 ms | 10 |

| (予約) | 11 | ||

外部クロックで駆動する場合、MCUの安定動作を確実にするために、供給クロック周波数が突然変化しないようにしなければなりません。連続するクロック・サイクルにおいて、2%以上の周波数変化がある場合、予期できない振る舞いを引き起こす可能性があります。もし、2%以上の周波数変化が必要な状況では、変化している時間帯においてMCUを確実にリセット状態にしてください。

システム・クロックのプリスケーラを、安定動作を保証した状態で、内蔵クロックの周波数変更を実行時に行うことが可能です。詳細については、「システム・クロックのプリスケーラ」(p.35)を参照してください。

デバイスは、CLK0端子からシステム・クロックを出力することができます。この出力を有効にするには、CKOUTヒューズ・ビットをプログラムしてください。このモードは、CPUのクロックを同一システム上の他の回路を駆動するのに適しています。クロック出力はリセット状態の期間も出力され、CKOUTヒューズ・ビットがプログラムされている場合は通常のI/O端子としての機能も無効になります。内蔵RC発振器を含む全てのクロック源において、CLKO端子に選択されたクロックを出力することができます。システム・クロックのプリスケーラが使用されている場合、分周されたシステム・クロックが出力となります。

デバイス中のタイマー/カウンター2は、外部の32.768kHz時計用クリスタルによるクロック、または外部クロック源により動作させることができます。タイマー/カウンター発振器の端子(TOSC1とTOSC2)は、XTAL1とXTAL2端子と同一端子を共有しています。これは、つまり、タイマー/カウンター発振器は、内蔵RC発振器がシステム・クロックとして使用されている場合にのみ使用可能であることを意味します。Figure 8-2 (p.29)のクリスタル発振子の接続方法を参照してください。

外部クロックをTOSC1端子に入力するには、ASSRレジスタのEXTCLKビットを1にする必要があります。32kHzクリスタルの代わりに外部クロックを選択する手順の詳細については、「タイマー/カウンター2の非同期動作モード」(p.150)をご覧ください。

ATega48/88/168には、システム・クロック用のプリスケーラがあり、「CLKPR - クロック分周レジスタ」(p.36)を設定することによってシステム・クロックを分周することができます。この機能により、システム・クロックの周波数を低く設定し、プロセッサの処理能力が低くても良い場合に消費電力を低くすることが可能になります。この機能は全てのクロック源設定において使用でき、CPUおよび全ての同期周辺回路のクロックに影響します。clkI/O, clkADC, clkCPU, clkFLASH はTable8-14 (p.37)に示された分周比で分周されます。

プリスケーラの設定を変更するとき、システム・クロックのプリスケーラは、システム・クロックに異常なパルスが発生しないように動作します。また、変更前、変更後のいずれのクロック周波数よりも高い中間周波数が発生しないように動作します。プリスケーラを構成するリップル・カウンターは分周されていないクロックで動作しており、CPUのクロック周波数よりも高い場合があります。したがって、プリスケーラの状態をある状態に確定させることは可能ではありません - たとえ、プリスケーラが読み取り可能であっても、プリスケーラが一つの分周クロックから、別の分周クロックに切り換わる正確な時間を予測することはできないということです。CLKPSの値が書き込まれた時刻から、変更後のクロック周波数が有効になるまでに、T1 + T2、ないしT1 + 2 * T2の時間が経過します。この間に、2つの有効なクロック・エッジが生じます。したがって、T1は変更前のクロック周期に相当し、T2は変更後のプリスケーラ設定でのクロック周期に相当します。

意図しないクロック周波数の変動を防止するため、CLKPSビットの変更では特別な手順を守る必要があります。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x66) | CAL7 | CAL6 | CAL5 | CAL4 | CAL3 | CAL2 | CAL1 | CAL0 | OSCCAL |

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | デバイス固有の調整値 | ||||||||

発振器調整値レジスタは調整済みRC発振器の微調整を行い、発振周波数に起因する動作速度の変動を抑制します。プログラム済みの調整値は自動的にチップのリセット時に書き込まれ、Table 28-1 (p.305) に規定された工場内調整済み周波数を得ることができます。アプリケーション・ソフトウェアで、このレジスタに書き込みを行い、発振周波数を変更することができます。Table 28-1 (p.305)に示されたとおりに発振器の周波数を調整することができます。指定範囲外の調整値での動作は保証されていません。

この発振器はEEPROMおよびフラッシュ・メモリの書き込みアクセスのタイミング計測に使用されており、書き込み時間が調整値の変更により変化することにご注意ください。EEPROMやフラッシュ・メモリに書き込みを行う場合、8.8MHzよりも大きな値に調整値を変更しないでください。そうでないと、EEPROMやフラッシュ・メモリへの書き込みに失敗する可能性があります。

CAL7ビットは、発振器の動作する周波数範囲を決定します。このビットを0に設定すると低い範囲の周波数に、1に設定すると高い範囲の周波数となります。この2つの周波数範囲は互いに重なっており、別の表現をすれば、OSCAL = 0x7Fの設定での周波数は、OSCCAL = 0x80の設定での周波数よりも高くなります。

CAL6..0ビットは、選択された範囲内で周波数を調整するために使用します。0x00の設定は、その範囲内でもっとも低い周波数となり、0x7Fは範囲内でもっとも高い周波数となります。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x61) | CLKPCE | - | - | - | CLKPS3 | CLKPS2 | CLKPS1 | CLKPS0 | CLKPR |

| Read/Write | R/W | R | R | R | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 各ビットの説明を参照 | ||||

CLKPSの各ビットの変更を有効にするには、CLKPEビットに1を書き込まなければなりません。CLKPRレジスタの他のビットに同時に0を書き込まれた場合にのみ、CLKPCEビットが更新されます。CLKPCEは、書き込み後4サイクル経過後、または、CLKPSビットが書き込まれた場合に、ハードウェアによりクリアされます。このタイムアウト期間以内にCLKPCEビットに再書き込みを行っても、タイムアウト時間は延長されず、またCLKPCEビットもクリアされません。

これらのビットにより、選択したクロック源に対する内部システム・クロックの分周比を指定します。これらのビットに書き込みを行って、実行中に動作周波数を変更するようなアプリケーションに利用することができます。分周器はMCUに入力される主クロックを分周するため、全ての同期して動作する周辺回路の動作は分周にともない遅くなります。Table 8-14に分周比を示します。

CKDIV8ヒューズ・ビットは、CLKPSビットの初期値を決定します。CKDIV8がプログラムされていない場合、CLKPSビットは"0000"にリセットされます。CKDIV8がプログラムされている場合、CLKPSビットは"0011"にリセットされ、スタートアップ時の分周比として8が有効になります。この機能は、選択したクロック源が、実装されている動作条件におけるデバイスの最大動作周波数よりも高い場合に使用してください。CKDIV8ヒューズ・ビットの設定に関係なく、いかなる値でもCLKPSビットに書き込みできることにご注意ください。選択したクロック源が、実装されている条件下でのデバイスの最大周波数よりも高い場合、アプリケーション・ソフトウェアによって十分な分周比が確実に設定されるようにしなければなりません。デバイスのCKDIV8ヒューズ・ビットはプログラムされた状態で出荷されます。

| CLKPS3 | CLKPS2 | CLKPS1 | CLKPS0 | クロック分周比 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 2 |

| 0 | 0 | 1 | 0 | 4 |

| 0 | 0 | 1 | 1 | 8 |

| 0 | 1 | 0 | 0 | 16 |

| 0 | 1 | 0 | 1 | 32 |

| 0 | 1 | 1 | 0 | 64 |

| 0 | 1 | 1 | 1 | 128 |

| 1 | 0 | 0 | 0 | 256 |

| 1 | 0 | 0 | 1 | (予約) |

| 1 | 0 | 1 | 0 | (予約) |

| 1 | 0 | 1 | 1 | (予約) |

| 1 | 1 | 0 | 0 | (予約) |

| 1 | 1 | 0 | 1 | (予約) |

| 1 | 1 | 1 | 0 | (予約) |

| 1 | 1 | 1 | 1 | (予約) |