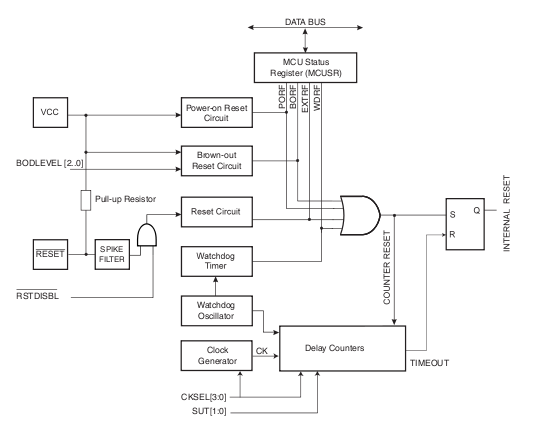

リセットが発生すると、すべてのI/Oレジスタは初期値に設定され、リセット・ベクトルからプログラム実行が開始されます。ATmega168では、リセット・ベクトルにある命令は必ずJMP(絶対ジャンプ)にして、リセット処理ルーチンへジャンプしなければなりません。ATmega48, ATmega88では、リセット・ベクトルにある命令は必ずRJMP(相対ジャンプ)にして、リセット処理ルーチンへジャンプしなければなりません。ただし、プログラムが割込みを無効にして全く使用しない場合、割込みベクトルは使用されず、これらの領域には通常のプログラムを配置することができます。これは、アプリケーション領域にリセット・ベクトル、割込みベクトルがブート領域にある場合、またはその逆の場合も同様です(ATmega88/168のみ)。Figure10-1の回路ブロック図はリセット回路の内容を表しています。Table28-3には、リセット回路の電気的特性が記されています。

AVRの入出力ポートはリセット要因がアクティブ状態になると即座に初期状態にリセットされます。この際、クロック源が動作している必要はありません。

全てのリセット要因が非アクティブになると、遅延カウンタが動作開始して内部リセット期間を延長します。これにより、電源が安定した電圧レベルに到達してから通常動作を開始することが可能になります。遅延カウンタのタイムアウト期間はSUTおよびCKSELヒューズ・ビットによって指定されます。「クロックの供給源」(p.27)に様々な遅延時間の設定方法が記載されています。

ATmega48/88/168 には4つのリセット要因があります。

Figure 10-1. リセット回路

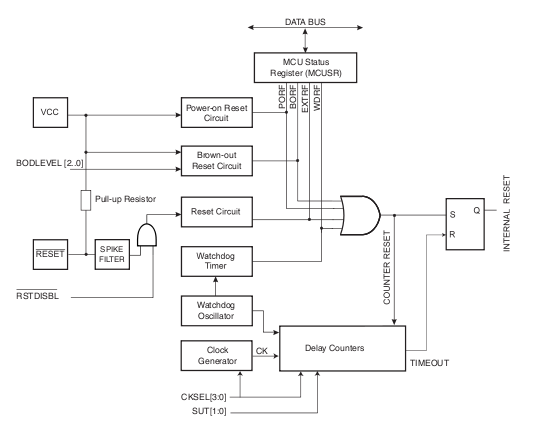

パワーオン・リセット(POR)のパルスは、内蔵の検出回路により生成されます。検出電圧レベルは、「システムおよびリセットの特性」(p.306)に記されています。PORはVCCが検出電圧レベルより低くなった場合は常に発生します。POR回路はスタートアップ・リセットの開始トリガーとして使用され、また、供給電圧の異常を検出するためにも使用されます。

パワーオン・リセット(POR)回路によりデバイスは電源投入時に確実にリセットされます。パワーオン・リセットのスレッショルド電圧に到達すると、遅延カウンタが始動してVCCの立ち上がりの後、どのくらいの時間デバイスをリセット状態に保持しておくかを決定します。VCCが検出電圧レベルよりも低下した場合、一切の遅延なしでRESET信号が再度アクティブ状態になります。

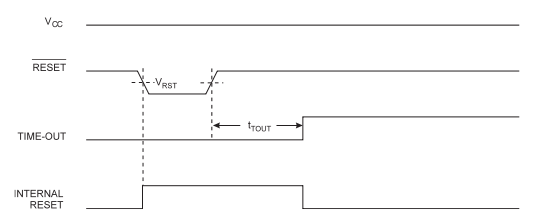

Figure 10-2. MCUスタートアップ動作、VCCに接続されたリセット信号

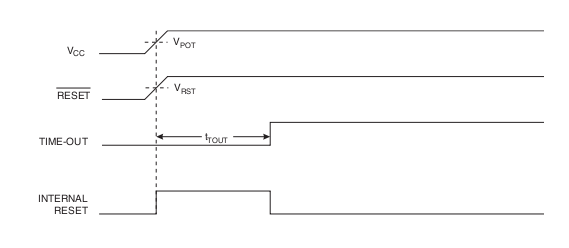

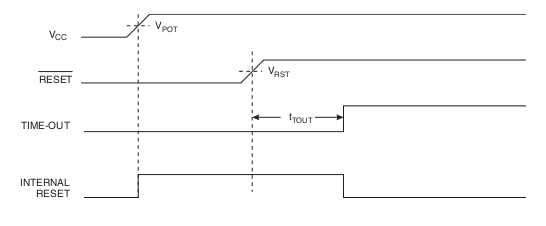

Figure 10-3. MCUスタートアップ動作、外部からのリセット延長

外部リセットは、RESET端子がLowレベルになることで発生します。既定の最小幅(「システムおよびリセットの特性」(p.306)参照)よりも長い時間のリセット・パルスにより、クロックが動作していない場合であってもリセットが発生します。短いパルスではリセットの発生は保証されません。印加された信号の立ち上がりにおいて、リセットのスレッショルド電圧(VRST)に到達したとき、タイムアウト時間(tTOUT)経過後に遅延カウンタによりMCUが始動します。外部リセットはRSTDISBLヒューズ・ビットにより無効にできます。Table 27-6 (p.286) を参照してください。

Figure 10-4. MCU動作中の外部リセット

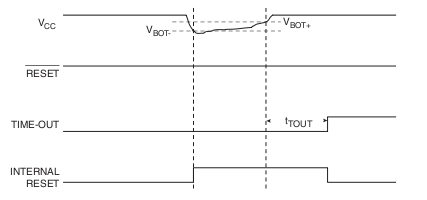

ATmega48/88/168 には内蔵のブラウン・アウト検出(BOD)回路があり、VCCの電圧を固定されたトリガー電圧とをMCUの動作中に比較して監視しています。BODのトリガー電圧レベルはBODLEVELヒューズ・ビットにより選択できます。トリガー電圧レベルにはヒステリシス特性があり、ブラウン・アウト検出においてスパイクが発生しないようになっています。検出レベルのヒステリシス特性は、VBOT+ = VBOT + VHYST/2 と VBOT- = VBOT - VHYST/2となっています。BODが有効になっているとき、VCCがトリガー電圧(Figure 10-5のVBOT+)よりも低い電圧になるとブラウン・アウト・リセットが即座に発生します。VCCがトリガー電圧(Figure 10-5のVBOT+)よりも高くなると、遅延カウンタがタイムアウト時間tTOUTの経過後、MCUを始動させます。

BOD回路は、「システムおよびリセットの特性」(p.306)に記されたtBODよりも長い時間、トリガー電圧レベルよりも低い状態になっている場合のみ、VCCの低下を検出します。

Figure 10-5. MCU動作中のブラウン・アウト・リセット

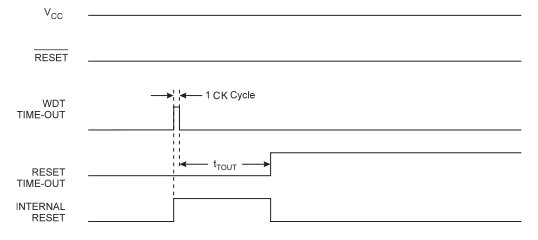

ウォッチドッグはタイムアウトしたときに、1CKサイクル期間の短いリセット・パルスを生成します。このパルスの立ち下がりで、遅延カウンタがタイムアウト時間tTOUTのカウントを開始します。詳細については、ウォッチドッグ・タイマー(p.48)を参照してください。

Figure 10-6. MCU動作中のウォッチドッグ・システム・リセット

ATmega48/88/168 には、内蔵のバンドギャップ電圧リファレンスが搭載されています。この電圧リファレンスはブラウン・アウト検出、および内蔵のアナログ・コンパレータへの入力やA/Dコンバータに使用されます。

電圧リファレンスにはスタートアップ時間があり、その影響を考慮して正しく使用する必要があります。「システムおよびリセットの特性」(p.306)にスタートアップ時間が記載されています。省電力を抑えるため、電圧リファレンスは常にオンになっているとは限りません。電圧リファレンスは次のような状況下でオンとなります。

したがって、BODが有効になっていない場合、ACBGビットの設定またはA/Dコンバータを有効に設定した後、ユーザーはアナログ・コンパレータの出力やA/Dコンバータの使用の前に電圧リファレンスを始動する必要があります。パワーダウン・モードでの消費電力を抑えるため、ユーザーは上記3つの条件が成立することを回避しておくことで、パワーダウン・モードに入る前に電圧リファレンスを確実にオフにしておくことができます。

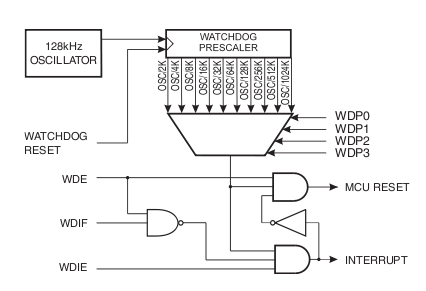

Figure 10-7. ウォッチドッグ・タイマー

ATmega48/88/168 には高機能のウォッチドッグ・タイマー(WDT)があります。WDTは独立した内蔵の128kHz発振器のクロックをカウントするタイマーです。WDTは、、指定されたタイムアウト値に達すると、割込み、あるいはシステム・リセットを発生させます。通常の動作モードでは、システムはWDR命令(ウォッチドッグ・タイマー・リセット)を使用して、カウンターがタイムアウト値に達する前に再スタートさせる必要があります。システムがカウンターを再スタートしない場合、割込み、あるいはシステム・リセットが発生します。

割込み動作モードでは、WDTはタイムアウト時に割込みを発生させます。この割込みにより、デバイスをスリープ・モードからウェークアップすることができ、また汎用のシステム・タイマーとして使用することもできます。使用の一例は、ある操作において最大時間を指定されている状況で、予想よりも長時間の操作を行った場合に割込みを発生させるような用途です。

システム・リセット動作モードでは、WDTはタイムアウト時にリセットを発生させます。これは、システムが正しく復帰しないコードによってハングアップするのを防止する典型的な用途に使用されます。

3番目の動作モード、割込み後システム・リセット動作モードでは、まず割込みを発生させ、その後システム・リセット動作モードに切り替える、他の二つの動作モードの組み合わせです。このモードにより、例えばシステム・リセットを行う前に重要なデータをセーブすることで安全なシャットダウンを行うようなことが可能になります。

ウォッチドッグ常時オン(WDTON)ヒューズ・ビットがプログラムされていると、ウォッチドッグ・タイマーを強制的にシステム・リセット動作モードに設定します。このヒューズ・ビットはシステム・リセット動作モード・ビット(WDE)と割込み動作モード・ビット(WDIE)をそれぞれ1、0に固定します。プログラムの安全性をさらに高めるためには、ウォッチドッグの設定変更を決められた時間と手順により設定します。WDEのクリアとタイムアウト設定の変更手順は次のようになります。

下記のアセンブリ言語、およびC言語のコーディング例はウォッチドッグ・タイマーをオフにする手順です。これらの例では、割込みは禁止されており(例えば、グローバル割込み許可ビットにより無効化)、この関数実行中には割込みが発生しないものという前提です。

| アセンブリ言語による例(1) |

|

| C言語による例(1) |

|

注意:

注意: 例えば不正なポインタによる暴走やブラウン・アウト状態などでウォッチドッグが意図していないのに有効になると、デバイスはリセットされウォッチドッグ・タイマーは有効にセットされたままとなります。プログラム中でウォッチドッグへの対処がされていない場合、タイムアウト・リセットによる無限ループに陥る可能性があります。このような状況を防止するため、ウォッチドッグを使用しない場合であっても、アプリケーション・ソフトウェアは必ずウォッチドッグ・システム・リセット・フラグ(WDRF)とWDEコントロール・ビットを初期化ルーチン内でクリアしておく必要があります。

下記のアセンブリ言語とC言語のコーティング例では、ウォッチドッグ・タイマーのタイムアウト時間を変更しています。

| アセンブリ言語による例(1) |

|

| C言語による例(1) |

|

注意:

注意: WDPビットの変更は、より短い値への変更の場合にタイムアウトを発生させる可能性があるため、WDPビットの変更の前に、ウォッチドッグ・タイマーをリセットする必要があります。

MCUステータスレジスタには、どのリセット要因によりMCUリセットが発生したかの情報が保持されています。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x35 (0x55) | - | - | - | - | WDRF | BORF | EXTRF | PORF | MCUSR |

| Read/Write | R | R | R | R | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 各ビットの説明を参照 | ||||

これらのビットはATmega48/88/168では未使用で、読み出し時には常にゼロとなります。

ウォッチドッグによるシステム・リセットが発生すると、このビットがセットされます。パワーオン・リセット時、または、このフラグにゼロを書き込むことでリセットされます。

ブラウン・アウト・リセットが発生すると、このビットがセットされます。パワーオン・リセット時、または、このフラグにゼロを書き込むことでリセットされます。

外部リセットが発生すると、このビットがセットされます。パワーオン・リセット時、または、このフラグにゼロを書き込むことでリセットされます。

パワーオン・リセットが発生すると、このフラグがセットされます。このビットは、ゼロを書き込むことでのみリセットされます。

各リセット・フラグを利用してリセット要因を特定するためには、ユーザープログラムにおいて、できるだけ早い段階でフラグを読み取り、その後MCUSRレジスタをリセットする必要があります。他のリセット要因が発生する前にMCUSRレジスタをクリアするようにすれば、リセットフラグを検査することによってリセット要因を特定することができます。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x60) | WDIF | WDIE | WDP3 | WDCE | WDE | WDP2 | WDP1 | WDP0 | WDTCSR |

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | X | 0 | 0 | 0 |

ウォッチドッグ・タイマーが割込み動作をするように設定されている場合、ウォッチドッグ・タイマーでタイムアウトが発生したときに、このフラグがセットされます。WDIFは対応する割込み処理ベクトルを実行した際に、ハードウェアによってクリアされます。別の方法として、WDIFに論理値1を書き込むことによりクリアすることもできます。SREGのIビットとWDIEビットがセットされている場合に、ウォッチドッグ・タイムアウト割込みが実行されます。

このビットに1が書き込まれていて、ステータス・レジスタのIビットがセットされているとき、ウォッチドッグ割込みが有効になります。この設定とともにWDEがクリアされている場合、ウォッチドッグ・タイマーは割込み動作モードになっており、タイムアウトがウォッチドッグ・タイマーで発生した時に対応する割込みが実行されます。

WDEがセットされている場合、ウォッチドッグ・タイマーは割込み後システム・リセット動作モードとなります。ウォッチドッグ・タイマーの最初のタイムアウトでWDIFがセットされます。対応する割込みベクトルを実行することにより、WDIEとWDIFがハードウェアにより自動的にクリアされます(その後、ウォッチドッグはシステム・リセット動作モードに移行します)。この動作はウォッチドッグ・タイマーの安全性を保ったまま、割込み処理を使用する際に便利です。割込み後システム・リセット動作モードのままにしておくには、WDIEを各割込みの後ごとにセットしてください。ただし、この処理はウォッチドッグのシステム・リセット動作モードの安全性を低下させる可能性があるため、割込み処理ルーチン内部で行うべきではありません。割込み処理が次のタイムアウト発生よりも前に実行されなければ、システム・リセット動作モードで動作します。

| WDTON(1) | WDE | WDIE | 動作モード | タイムアウト時の動作 |

|---|---|---|---|---|

| 1 | 0 | 0 | 停止 | なし |

| 1 | 0 | 1 | 割込み動作モード | 割込み発効 |

| 1 | 1 | 0 | システム・リセット動作モード | リセット発効 |

| 1 | 1 | 1 | 割込み後システム・リセット動作モード | 割込みを発効後、システム・リセット動作モードへ移行 |

| 0 | x | x | システム・リセット動作モード | リセット発効 |

注意: 1. WDTONヒューズ・ビットについて、“0“は「プログラムされている」、“1“は「プログラムされていない」ことを表します

このビットは、WDEおよび分周比設定の変更を行う処理時間の制限された手順内において使用します。WDEビットをクリアしたり、分周比を変更したり、その二つを同時に行うには、WDCEビットをセットしておかなければなりません。

1が書き込まれると、ハードウェアによりWDCEビットは4サイクル後にクリアされます。

WDEビットは、MCUSRレジスタのWDRFビットの内容が上書きされます。WDRFがセットされる時に、常にWDEがセットされることを意味します。WDEをクリアするには、WDRFをまずクリアしなければなりません。この機能により、エラーを発生させている条件が解消されない間に複数回のリセットが確実に起きるようにし、エラー後の安全なスタートアップ動作が可能になります。

WDP3..0 ビットにより、ウォッチドッグ・タイマーが動作におけるクロック分周比を決定します。Table 10-2 (p.54)に各分周比と、それに対応するタイムアウト時間を記します。

Table 10-2. ウォッチドッグ・タイマーの分周比選択

| WDP3 | WDP2 | WDP1 | WDP0 | WDT発振器のサイクル数 | VCC = 5.0V条件でのタイムアウト時間(typ) |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 2K (2048) サイクル | 16 ms |

| 0 | 0 | 0 | 1 | 4K (4096) サイクル | 32 ms |

| 0 | 0 | 1 | 0 | 8K (8192) サイクル | 64 ms |

| 0 | 0 | 1 | 1 | 16K (16384) サイクル | 0.125 s |

| 0 | 1 | 0 | 0 | 32K (32768) サイクル | 0.25 s |

| 0 | 1 | 0 | 1 | 64K (65536) サイクル | 0.5 s |

| 0 | 1 | 1 | 0 | 128K (131072) サイクル | 1.0 s |

| 0 | 1 | 1 | 1 | 256K (262144) サイクル | 2.0 s |

| 1 | 0 | 0 | 0 | 512K (524288) サイクル | 4.0 s |

| 1 | 0 | 0 | 1 | 1024K (1048576) サイクル | 8.0 s |

| 1 | 0 | 1 | 0 | (予約) | |

| 1 | 0 | 1 | 1 | ||

| 1 | 1 | 0 | 0 | ||

| 1 | 1 | 0 | 1 | ||

| 1 | 1 | 1 | 0 | ||

| 1 | 1 | 1 | 1 | ||