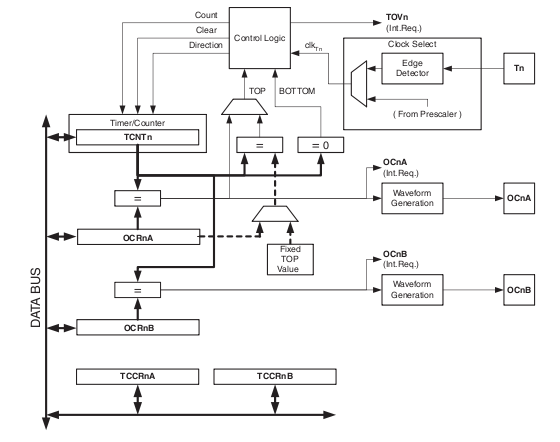

Figure 14-1. 8ビット タイマー/カウンター ブロック図

タイマー/カウンター0 は汎用の8ビットタイマー/カウンターモジュールで、2つの独立した出力比較ユニットとPWM機能を備えています。これを利用することで、正確なプログラム実行タイミング(イベント管理)や波形発生が可能になります。

8ビット タイマー/カウンターの簡略ブロック図は Figure 14-1 をご覧ください。実際の入出力端子の配置については、 「ピン接続図 ATmega48/88/168」(p.2)を参照してください。CPUがアクセス可能な入出力レジスタ、および各入出力ビット、入出力端子は太字で示されています。各デバイス固有の入出力レジスタとビットの配置は「レジスタ詳細」(p.100)を参照してください。

なお、「消費電力を最小にするために」(p.40)にあるように、タイマー/カウンター0 モジュールを有効にするためには、PRTIM0 ビットに0を書き込んでおかなければなりません。

このセクションでは、多くのレジスタと各ビットの名称は一般化された形式で記されています。小文字の"n"は、タイマー/カウンターの番号、この節では0となるものです。小文字の"x"は出力比較ユニットを、この節では比較ユニットAまた比較ユニットBとなるものです。プログラム中で各レジスタやビットの定義を用いる場合は、正しい形式を使用しなければなりません。例えば、タイマー/カウンター0のカウント値にアクセスする場合はTCNT0を用いる、などです。

Table 14-1 に示された用語も、データシート中で頻繁に使用されます。

| BOTTOM | カウンターが0x00になったときを、BOTTOMに達した、といいます。 |

| MAX | カウンターが0xFF(10進で255)になったときを、MAXに達した、といいます。 |

| TOP | カウンターが、そのカウント動作において最大値に達したときを、TOPに達したといいます。TOPの値は固定値0xFF(MAX)に設定するか、OCR0Aレジスタの値に設定することが可能です。設定は動作モードによって異なります。 |

タイマー/カウンター(TCNT0)、および出力比較レジスタ(OCR0A と OCR0B) は8ビットのレジスタです。割り込み要求(Int.Req.と図中では省略)信号はすべてタイマー割り込みフラグ・レジスタ (TIFR0) から参照可能です。すべての割り込みはタイマー割り込みマスク・レジスタ (TIMSK0) によって、個別に有効・無効の設定が可能です。TIFR0 と TIMSK0 は図中には描かれていません。

タイマー/カウンターはプリスケーラーを経由した内部クロックをカウントするか、T0端子に供給される外部クロックによってカウント動作を行います。クロック選択ブロックはどのクロック源、および、どのクロックエッジによって、タイマー/カウンターがアップ・カウント(またはダウン・カウント)動作をするかを制御します。タイマー/カウンターはクロック源が選択されていない場合は休止しています。クロック選択ブロックからの出力はタイマークロック(clkT0)という名称で呼びます。

二重バッファを備えた比較レジスタ (OCR0A と OCR0B) は、タイマー/カウンターの値と常に比較され、比較結果は波形発生器が比較一致出力端子 (OC0A と OC0B) に、PWM出力や可変周波数出力を発生させるために使用されます。詳細については、「比較ユニットの使い方」(p.92)(訳注:ページ、リンク先訂正)を参照してください。比較が一致した際には比較フラグ (OCF0A または OCF0B) がセットされ、比較一致割り込み要求を発生させるために使用されます。

タイマー/カウンターは内部または外部のクロック源で動作します。クロック源の選択は、タイマー/カウンターコントロールレジスタ(TCCR0B)中のクロック選択ビット(CS02:0)によって制御されるクロック選択回路によって選択されます。クロック源とプリスケーラの詳細については、「タイマー/カウンター0、およびタイマー/カウンター1のプリスケーラ」(p.136)を参照してください。

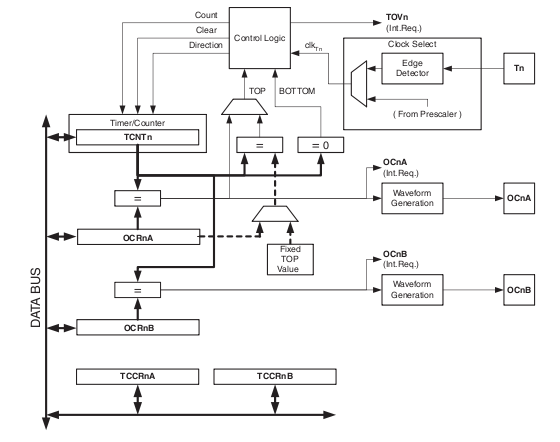

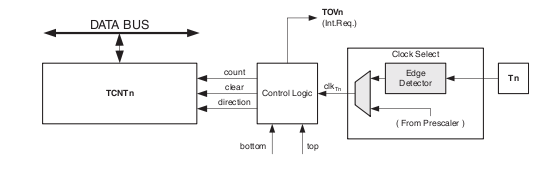

8ビット タイマー/カウンターの中心部はプログラマブル双方向カウンターユニットです。Figure 14-2 は、カウンターと周辺回路のブロック図です。

| count | TCNT0 を1だけ、アップ・カウントまたはダウン・カウントする |

|---|---|

| direction | アップ・カウント、ダウン・カウントの方向選択 |

| clear | TCNT0 のクリア(全ビットを0にセット) |

| clkTn | タイマー/カウンターのクロック。ここでは、clkT0と記載 |

| top | TCNT0 が最大値に達した、という信号を発生 |

| bottom | TCNT0 が最小値(0)に達した、という信号を発生 |

使用している動作モードに応じて、カウンターの値はクロック(clkT0)ごとに、クリア、インクリメント、またはデクリメントされます。clkT0は外部または内部のクロック源から生成され、クロック選択ビット(CS02:0)によって選択されます。クロックが選択されていない場合(CS02:0 = 0)、タイマーは停止しています。ただし、clkT0クロックの有無に関わらず、TCNT0の値はCPUからアクセス可能です。CPUによる書き込みは、すべてのカウンターのクリア、またはカウント動作を上書きします(CPUによる書き込みが優先されます)。

一連のカウント動作(カウント・シーケンス)は、タイマー/カウンターコントロールレジスタ (TCCR0A) 中の WGM01 および WGM00 ビット、タイマー/カウンターコントロールレジスタB (TCCR0B) 中の WGM02 ビットによって決まります。カウンターのカウント・シーケンスと、比較ユニットの OC0A および OC0B 出力に発生する波形には密接な関係があります。カウント・シーケンスと波形発生についての、より高度な詳細内容については「動作モード」(p.93)をご覧ください。

タイマー/カウンター・オーバーフロー・フラグ (TOV0) は WGM02:0 によって選択される動作モードに応じてセットされます。TOV0 フラグはCPUへの割り込みを発生するために使用できます。

8ビットの比較一致検出回路によって、常に TCNT0 と比較レジスタ (OCR0A、およびOCR0B) の値が比較されます。TCNT0 と OCR0A、またはOCR0B の値が一致したとき、一致検出回路は信号を発生します。一致検出信号によって、次のクロックサイクルで、一致フラグ (OCF0A または OCF0B) がセットされます。対応する割り込みが有効になっている場合、一致フラグによって比較一致割り込みが発生します。割り込みが実行されると、一致フラグは自動的にクリアされます。別の方法として、ソフトウェアによって、対応するフラグのI/Oアドレスに論理値1を書き込むことで、一致フラグをクリアすることも可能です。波形発生器は比較一致信号を利用して、 WGM02:0 ビット、および比較一致出力モード・ビット(COM0x1:0)によって設定されている動作モードに応じた出力を発生させます。最大(max)および最小(bottom)信号は、波形発生器が特定の動作モードで、タイマーの極大値・極小値での動作を決定するために利用されます(「動作モード」(p.93)を参照)。

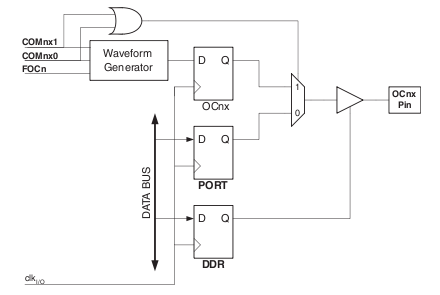

Figure 14-3 に出力比較ユニットのブロック図を示します。

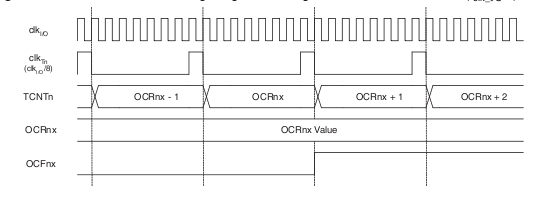

PWMモードを使用している場合には、OCR0x レジスタは二重バッファが有効になっています。通常モードとクリア・タイマー・オン・コンペア(CTC)モードでは、二重バッファは無効になっています。二重バッファによって、OCR0x 比較レジスタの更新を、カウント・シーケンスの top値、または bottom値のいずれかに同期させて行います。この同期で、不揃いな長さの非対称なPWMパルスが発生することを防止し、出力に異常パルス(グリッチ)が現れなくなります。

この比較レジスタOCR0xへのアクセスは複雑に思えるかもしれませんが、そうではありません。二重バッファが有効になっていればCPUは比較レジスタのバッファにアクセスし、無効になっている場合、CPUは直接比較レジスタ OCR0xにアクセスするということです。

PWM波発生モードではない場合、強制一致ビットに1を書き込むことにより、比較回路の一致出力を強制的に「一致したとする」ことができます。強制的に一致したとすることでは、比較一致フラグはセットされず、またタイマーの再ロードやクリアも行われません。しかし、OC0x端子の状態は、実際に比較結果が一致したかのように更新されます(COM0x1:0 ビットの設定によって、OC0x 端子がセット、リセットまたは反転するのかが決まります)。

TCNT0レジスタへのCPUの書き込み動作は、どのような場合でも、その直後のタイマーのクロックサイクルで起きるはずの比較一致を阻止します。これはタイマーが停止している場合でも同じです。この機能により、タイマー/カウンターを有効にした途端に割り込みを発生させることなく、OCR0x レジスタを TCNT0 レジスタと同じ値に初期化することが可能になります。

TCNT0への書き込み動作によって、あらゆる比較一致が1タイマークロックサイクルの間、無効になるため、比較ユニットを使用している状態でTCNT0の値を変更すると、タイマー/カウンターが動作しているかどうかに関係なく、問題が発生する可能性があります。もしTCNT0に書き込まれた値がOCR0xと同じ値であったとすると、(書き込みにより無効になっているため)比較一致が検出されず、結果として意図しない波形出力が発生します。同様に、ダウンカウントをしている TCNT0 に、BOTTOM(最小値)と同じ値を書き込んではいけません。

OC0xの設定は、入出力方向レジスタに該当ポートの端子の出力設定を行う前に実行する必要があります。通常モードでOC0xの値を設定する一番簡単な方法は、強制一致ストローブ・ビットを使用することです。これにより、OC0xレジスタの値は、波形発生モードを別のモードに変更する場合でも、正しく保持されます。

COM0x1:0 ビットは比較する値とは異なり、二重バッファになっていないことに注意してください。COM0x1:0 ビットへの変更は即座に動作に反映されます。

比較一致出力モードビット Compare Output mode (COM0x1:0) には二つの機能があります。波形発生器は COM0x1:0 ビットを使用して比較一致出力 (OC0x) の次回の比較一致時の状態を定義しています。また、COM0x1:0 ビットは OC0x 出力端子にどの信号を出力するかの設定にも使用されます。Figure 14-4 に、COM0x1:0 ビットの設定によって影響を受ける論理回路の簡略化した回路図を示します。図中において、I/O レジスタ、I/O ビット、および I/O 入出力端子は太字で示されています。汎用I/Oポートのコントロールレジスタ(DDRおよびPORT)のうちCOM0x1:0 ビットによって影響を受けるもののみが描かれています。OC0x の状態を参照する際に対象となるのは、内部の OC0x ビット・レジスタであって、OC0x 端子の状態ではありません。システム・リセット時には OC0x ビット・レジスタはゼロにリセットされます。

汎用入出力ポートの機能は、COM0x1:0 ビットのいずれかがセットされている場合、波形発生器の比較出力(OC0x)の接続が優先されます。しかし、OC0x端子の入出力方向(設定が入力端子か、出力端子か)は、入出力方向レジスタ(DDR)によって対象となる端子の入出力方向が制御されています。入出力方向レジスタのOC0x端子(DDR_OC0x)の設定ビットは、OC0xの値が端子に反映されるよりも以前に、出力として設定されていなければなりません。ポートの端子機能の切り替えは、波形発生器のモードとは無関係です。

この比較回路出力端子の設計によって、OC0xの状態を初期化してから出力を有効にすることが可能になります。COM0x1:0ビットの設定は特定の動作モードでは(将来拡張)予約となっていることに注意してください。詳しくは、「レジスタ詳細」(p.100)をご覧ください。

波形発生器は、ノーマル、CTC、PWMモードの各モードで、COM0x1:0ビットを異なる意味に使っています。すべてのモードにおいて、COM0x1:0 = 0 は波形発生器に対して、OC0xレジスタが次回の比較一致の際に何もしない、という設定です。PWM以外のモードでの、比較一致の際のアクションについては、Table 14-2 (p.100)を参照してください。高速PWMモードについては、Table 14-3 (p.100)を、位相補正PWMモードについては、Table 14-4 (p.101)を参照してください。

COM0x1:0ビットの状態変更は、ビット書き込み後の最初の比較一致時の動作に影響があります。PWM以外のモードでは、FOC0x ストローブ・ビットを使用することで、強制的に一致時のアクションを発生させることが可能です。

動作モード(タイマー/カウンターと比較一致出力端子の挙動)は、波形発生モード(WGM02:0ビット)と比較一致出力モード(COM0x1:0ビット)の組み合わせによって定義されます。比較一致出力モードビットの内容は、カウント・シーケンスに影響を与えません。カウント・シーケンスに影響があるのは、波形発生モードビットです。COM0x1:0ビットはPWM出力を反転出力(反転PWM波)とするか非反転出力(非反転PWM波)とするか、を設定します。PWM以外のモードでは、COM0x1:0ビットは出力をセットするか、クリアするか、または、反転(トグル)するかを設定します。(「比較一致出力ユニット」(p.92)を参照してください。)

動作タイミングの詳細な情報については、「タイマー/カウンター タイミング・ダイアグラム」(p.98)を参照してください。

通常モード(設定 WGM02:0 = 0)はもっとも単純な動作モードです。このモードでは、カウント動作の方向は常にアップカウント(インクリメント動作)で、カウンターのクリアは行われません。カウンターは8ビットの最大値(TOP = 0xFF)を単純に通過し、最小値(0x00)から再度カウントを続けます。通常モードにおいて、タイマー/カウンター・オーバーフロー・フラグ(TOV0)はTCNT0がゼロになるのと同一のタイマー・クロック・サイクルにおいてセットされます。このとき、TOV0フラグは、セットのみされクリアされない、という点をのぞいて、9番目のビットのように振る舞います。しかし、タイマー・オーバーフロー割り込みと組み合わせ、TOV0フラグを自動的にクリアするようにすると、タイマーの精度をソフトウェアによって増加させることが可能です。通常モードにおいては、カウンターに新しい値をいつでも書き込み可能で、特別な状況を想定する必要はありません。

比較出力ユニットを使用して、特定の時間で割り込みを発生させるように設定することが可能です。通常モードで、比較一致出力を波形発生のために使用することは推奨されません。なぜなら、それを実現するためには多くのCPU時間を必要とするからです。

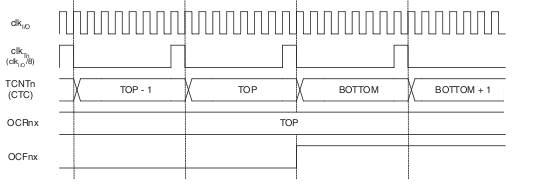

CTCモード (WGM02:0 = 2)では、OCR0A レジスタはカウンターの精度を操作するために使用します。CTCモードでは、カウンターはTCNT0の値がOCR0Aレジスタの値と等しくなった際にクリアされます。OCR0Aレジスタはカウンターの最大値を定義しており、したがって、その値がカウンターの精度となります。このモードを使用することで、比較一致出力の周波数を広範囲にわたって制御することが可能となります。また、外部イベントのカウント動作を簡単に行うこともできます。

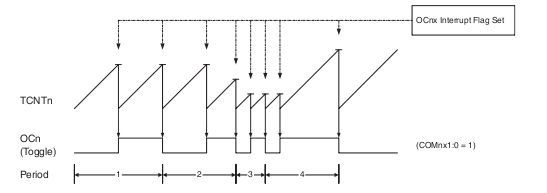

CTCモードのタイミング・ダイアグラムはFigure 14-5に示されています。カウンターの値(TCNT0)はTCNT0とOCR0Aの比較一致が発生するまで増加し、その後カウンター(TCNT0)がクリアされます。

割り込みは、OCF0Aフラグを使用することで、カウンターの値が最大値(TOP)に達する度に発生させることが可能です。割り込みが有効になっていれば、割り込み処理ルーチン内で、最大値(TOP)の値設定を更新する、という使い方ができます。しかし、カウンターがプリスケーラなし、または、分周比の小さいプリスケーラで動作している時に、最大値(TOP)を最小値(BOTTOM)に近い値に更新するのには注意が必要です。なぜなら、CTCモードでは、二重バッファ機能は無効になっているためです。もし、OCR0Aに新たに書き込まれた値が、現時点でのTCNT0の値よりも小さかったら、カウンターは比較一致に失敗することになります。その場合、カウンターは最大値(0xFF)までカウントして0x00からスタートし、もう一周してから、比較一致が発生することになります。

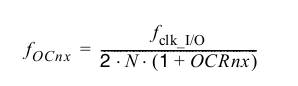

波形出力をCTCモードで使用するためには、比較一致出力モードビットをトグル・モード(COM0A1:0 = 1)に設定することで、OC0A出力が比較一致が起こる度に状態を反転(トグル)するように設定できます。OC0Aの値は、その端子の入出力方向が出力に設定されていなければ、出力端子に反映されません。生成される波形は、OCR0Aがゼロ(0x00)に設定されているとき、最大周波数 fOC0 = fclk_I/O/2 となります。波形の周波数は以下の式で計算されます。

Nの値はプリスケーラの分周比(1, 8, 64, 256, または 1024)を表します。

通常モードと同様に、TOV0フラグはカウンターのカウント値がMAX値から0x00になるのと同じタイマー・クロック・サイクルでセットされます。

高速PWMモード(WGM02:0 = 3 または 7)では、高い周波数でのPWM波を発生させることが出来ます。高速PWMモードは、位相補正PWM動作モードとは、片方向カウントの動作である点が異なります。カウンターはBOTTOMからTOPまでカウントを行い、再びBOTTOMからカウントを再開します。TOPの値は、WGM2:0 = 3のとき0xFF、WGM2:0 = 7のとき OCR0A の値、と定義されます。比較一致が非反転出力モードのとき、比較一致出力(OC0x)はTCNT0とOCR0xの値が一致したときにクリアされます。反転出力モードでは、比較一致の時に出力はセットされ、BOTTOMに達したときにクリアされます。片方向カウント動作のため、高速PWMモードの動作周波数は双方向カウント動作である位相補正PWMモードと比較して二倍の周波数にすることができます。このように高い動作周波数のため、高速PWMモードは電源の安定化、整流動作やD/Aコンバーターなどの応用に適しています。高い周波数での動作によって、外形寸法の小さな部品(コイル、コンデンサ)を用いることができ、したがってシステム全体のコストを削減することができます。

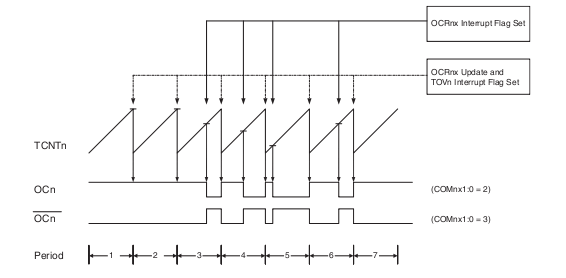

高速PWMモードでは、カウンターはTOPの値と等しくなるまでインクリメントされ、そして次のタイマークロックサイクルでクリアされます。高速PWMモードのタイミング・ダイアグラムをFigure 14-6に示します。ダイアグラム中では、TCNT0の値が片方向カウント動作であることを表すグラフになっていることがわかります。タイミング・ダイアグラムには、非反転および反転PWM出力もあわせて描かれています。小さな水平線で示されたTNT0の斜め線上の位置はOCR0xとTCNT0の値が一致したことを表しています。

タイマー/カウンター・オーバーフローフラグ(TOV0)は、カウンターがTOPの値に到達すると毎回セットされます。割り込みが有効になっていれば、割り込み処理ルーチン内で比較レジスタの値を更新することが可能です。

高速PWMモードでは、比較ユニットによってOC0x端子にPWM波出力を発生させることが出来ます。COM0x1:0ビットの設定を2にすることで非反転PWM出力を、COM0x1:0ビットの設定を3にすることで反転PWM出力を生成します。WGM02ビットがセットされていれば、COM0A1:0ビットを1に設定すると、OC0A端子を比較一致時にトグル(反転)動作させることができます。この反転動作はOC0B端子には備わっていません(Table 14-6 (p.101)を参照)。実際のOC0xの値がポート端子に反映されるのは、該当端子の入出力方向の設定が出力設定になっている場合だけです。比較一致時にOC0xレジスタのセット(またはクリア)が行われ、カウンターがクリアされる(TOP値からBOTTOM値に更新)タイマークロックサイクルにおいて、OC0xレジスタがクリア(またはセット)されることによって、PWM波出力が発生します。

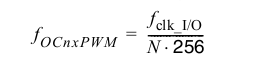

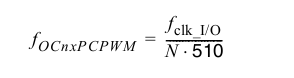

PWM波出力周波数は次式で計算できます。

Nの値はプリスケーラの分周比(1, 8, 64, 256, or 1024)を表します。

PWM波出力を高速PWMモードで発生させているときに、OCR0Aレジスタに極端な値を設定すると特殊な状態の出力となります。OCR0AレジスタがBOTTOM値と同じ値に設定されると、(MAX+1)タイマークロックサイクルごとに短い幅のスパイク状のパルスが出力として現れます。OCR0Aレジスタの値をMAXと同じ値に設定すると、常にHiまたはLow(COM0A1:0 ビットによって設定された出力の極性により異なります)の出力となります。

高速PWMモードで可変周波数出力(50%デューティー比)を得るには、OC0xレジスタの設定を比較一致のたびに、論理値をトグル(反転)するように設定(COM0x1:0 = 1)することで可能です。この場合、出力の最大周波数は、OCR0Aがゼロに設定されたときで、 fOC0 = fclk_I/O/2 となります。この機能は、高速PWMモードでは二重バッファが有効になっているという点以外は、CTCモードでのOC0Aのトグル(反転)動作と同様のものです。

位相補正PWMモードでは、高精度の位相補正されたPWM波出力を可能にします。位相補正PWMモードは、双方向カウントで動作します。カウンターはBOTTOM値からTOP値へ、そしてTOP値からBOTTOM値へと繰り返しカウントを行います。TOP値はWGM2:0 = 1のとき0xFF、 WGM2:0 = 5のときOCR0Aの値と定義されます。非反転比較一致出力モードでは、一致出力(OC0x)は、アップカウント時ではTCNT0とOCR0xの比較一致時にクリアされ、ダウンカウント時でセットされます。反転一致出力モードでは、論理を反転した動作となります。双方向カウント動作は、片方向カウント動作とくらべて、最大周波数は低くなりますが、双方向カウントによるPWMモードの対称的な動作のため、このモードはモーターの制御に適しています。

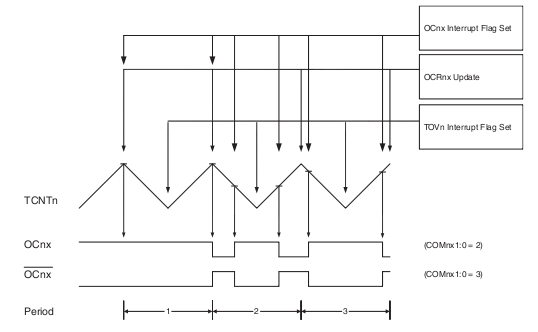

位相補正PWMモードでは、カウンターはTOP値までインクリメントされ、TOP値に達したとき、カウント方向を変更します。TCNT0の値は1タイマークロックサイクルの期間、TOPの値と等しくなります。位相補正PWMモードのタイミング・ダイアグラムをFigure 14-7に示します。タイミング・ダイアグラム中で、TCNT0の値は双方向カウント動作のグラフとして示されています。タイミング・ダイアグラムには、非反転および反転PWM出力もあわせて描かれています。小さな水平線で示されたTNT0の傾斜線上の位置はOCR0xとTCNT0の値が一致したことを表しています。

タイマー/カウンター・オーバーフローフラグ(TOV0)は、カウンターがBOTTOMの値に到達すると毎回セットされます。割り込みフラグを用いて、カウンターがBOTTOM値に達するたびに割り込みを発生させることが出来ます。

位相補正PWMモードでは、比較ユニットによってOC0x端子にPWM波出力を発生させることが出来ます。COM0x1:0ビットの設定を2にすることで非反転PWM出力を、COM0x1:0ビットの設定を3にすることで反転PWM出力を生成します。COM0A1:0ビットを1に設定すると、WGM02ビットがセットされていれば、OC0A端子を比較一致時にトグル(反転)動作させることができます。この反転動作はOC0B端子には備わっていません(Table 14-7 (p.102)を参照)。実際のOC0xの値をポート端子に反映されるのは、該当端子の入出力方向の設定が出力設定になっている場合だけです。 アップカウント中のTCNT0とOCR0xの比較一致時にOC0xレジスタのセット(またはクリア)が行われ、ダウンカウント中のTCNT0とOCR0xの比較一致時にOC0xレジスタがクリア(またはセット)によって、PWM波出力が発生します。

位相補正PWM波での出力周波数は次式で計算できます。

Nの値はプリスケーラの分周比(1, 8, 64, 256, 1024)を表します。

PWM波出力を位相補正PWMモードで発生させているときに、OCR0Aレジスタに極端な値を設定すると特殊な状態の出力となります。非反転出力モードでは、OCR0AレジスタがBOTTOM値と同じ値に設定されると、出力は常にLowとなり、MAX値と同じ値に設定すると常にHiとなります。反転出力モードでは、論理値を逆転した出力になります。

Figure 14-7において、周期2の最初において、比較一致が起こらないにもかかわらず、OCnxが HiからLowへ変化しています。この出力変更はBOTTOM値の前後において、対称性を確保するためのものです。比較一致がないのに出力が変化するケースは、以下の二つあります。

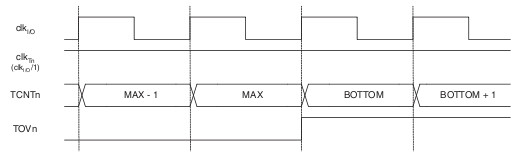

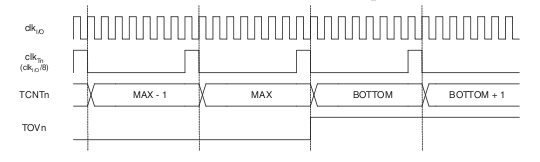

タイマー/カウンターは同期カウンタであるため、タイマークロック(clkT0)は以下の図においてクロック・イネーブル信号として示されています。各図は割り込みフラグがいつセットされるのか、ということをあわせて描かれています。Figure 14-8は、タイマー/カウンターの基本的な動作についてのタイミング・データを含んでいます。図は位相補正PWMモード以外のすべてのモードにおいて、MAX値に近い部分のカウントシーケンスを示しています。

Figure 14-9 はプリスケーラが有効になっている点以外は、同じタイミング・データを示しています。

Figure 14-10 は、OCR0AがTOPとして設定されている場合の、すべてのモードにおけるOCF0Bフラグのセット、およびCTCモードとPWMモードを除くすべてのモードにおけるOCF0Aフラグのセットについて描かれています。

Figure 14-11は、OCR0AがTOPとして設定されている場合の、CTCモードとPWMモードにおけるOCF0AフラグのセットとTCNT0のクリアについて描かれています。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x24 (0x44) | COM0A1 | COM0A0 | COM0B1 | COM0B0 | - | - | WGM01 | WGM00 | TCCR0A |

| Read/Write | R/W | R/W | R/W | R/W | R | R | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

このビットは比較一致出力端子(OC0A)の動作を制御します。一つ、または二つのCOM0A1:0ビットがセットされると、OC0A出力が優先され、接続されている入出力端子の通常のI/Oポート機能は無効になります。ただし、データ方向レジスタ(DDR)のOC0A端子に対応するビットは、出力が有効になるように設定されていなければなりません。

OC0A信号が端子に接続されている場合、COM0A1:0ビットの機能は、WGM02:0ビットの設定によって変わります。Table 14-2に、WGM02:0ビットが通常モード、またはCTCモード(つまりPWM以外のモード)に設定されている場合の、COM0A1:0ビットの機能を示します。

Table 14-2. 比較一致出力モード (PWMモード以外)

| COM0A1 | COM0A0 | 内容 |

|---|---|---|

| 0 | 0 | 通常のポートとしての動作。OC0A信号は非接続 |

| 0 | 1 | OC0A端子を比較一致の際にトグル(反転) |

| 1 | 0 | OC0A端子を比較一致の際にクリア |

| 1 | 1 | OC0A端子を比較一致の際にセット |

Table 14-3に、WGM01:0ビットが高速PWMモードに設定されている場合の、COM0A1:0ビットの機能を示します。

Table 14-3. 比較一致出力モード (高速PWMモード)

| COM0A1 | COM0A0 | 内容 | ||||

|---|---|---|---|---|---|---|

| 0 | 0 | 通常のポートとしての動作。OC0A信号は非接続 | ||||

| 0 | 1 |

|

||||

| 1 | 0 | OC0A端子を比較一致でクリアし、BOTTOM値の際にセットする(非反転モード) | ||||

| 1 | 1 | OC0A端子を比較一致でセットし、BOTTOM値の際にクリアする(非反転モード) |

注意:1 OCR0AがTOP値と同じでCOM0A1がセットされている場合は、特殊なケース。この場合、比較一致は無視されるが、BOTTOMでのセット、またはクリアは実行される。「高速PWMモード」(p.95)を参照。

Table14-4に、WGM02:0ビットが位相補正PWMモードに設定されている場合の、COM0A1:0ビットの機能を示します。

Table 14-4. 比較一致出力モード (位相補正PWMモード)

| COM0A1 | COM0A0 | 内容 | ||||

|---|---|---|---|---|---|---|

| 0 | 0 | 通常のポートとしての動作。OC0A信号は非接続 | ||||

| 0 | 1 |

|

||||

| 1 | 0 | OC0A端子をアップカウント動作中の比較一致でクリアし、ダウンカウント中の比較一致でセットする | ||||

| 1 | 1 | OC0A端子をアップカウント動作中の比較一致でセットし、ダウンカウント中の比較一致でクリアする |

注意:1 OCR0AがTOP値と同じでCOM0A1がセットされている場合は、特殊なケース。この場合、比較一致は無視されるが、TOPでのセット、またはクリアは実行される。詳細は、「位相補正PWMモード」(p.96)を参照。

このビットは比較一致出力端子(OC0B)の動作を制御します。一つ、または二つのCOM0B1:0ビットがセットされると、OC0B出力が優先され、接続されている入出力端子の通常のI/Oポート機能は無効になります。ただし、データ方向レジスタ(DDR)のOC0B端子に対応するビットは、出力が有効になるように設定されていなければなりません。

OC0B信号が端子に接続されている場合、COM0B1:0ビットの機能は、WGM02:0ビットの設定によって変わります。Table 14-5に、WGM02:0ビットが通常モード、またはCTCモード(つまりPWM以外のモード)に設定されている場合の、COM0B1:0ビットの機能を示します。

Table 14-5. 比較一致出力モード (PWMモード以外)

| COM0B1 | COM0B0 | 内容 |

|---|---|---|

| 0 | 0 | 通常のポートとしての動作。OC0B信号は非接続 |

| 0 | 1 | OC0B端子を比較一致の際にトグル(反転) |

| 1 | 0 | OC0B端子を比較一致の際にクリア |

| 1 | 1 | OC0B端子を比較一致の際にセット |

Table 14-6に、WGM02:0ビットが高速PWMモードに設定されている場合の、COM0B1:0ビットの機能を示します。

Table 14-6. 比較一致出力モード (高速PWMモード)

| COM0B1 | COM0B0 | 内容 | ||||

|---|---|---|---|---|---|---|

| 0 | 0 | 通常のポートとしての動作。OC0B信号は非接続 | ||||

| 0 | 1 |

|

||||

| 1 | 0 | OC0B端子を比較一致でクリアし、BOTTOM値の際にセットする(非反転モード) | ||||

| 1 | 1 | OC0B端子を比較一致でセットし、BOTTOM値の際にクリアする(反転モード) |

注意:1 OCR0BがTOP値と同じでCOM0B1がセットされている場合は、特殊なケース。この場合、比較一致は無視されるが、BOTTOMでのセット、またはクリアは実行される。95ページの「高速PWMモード」を参照。

Table14-7に、WGM02:0ビットが位相補正PWMモードに設定されている場合の、COM0B1:0ビットの機能を示します。

Table 14-7. 比較一致出力モード (位相補正PWMモード)

| COM0B1 | COM0B0 | 内容 |

|---|---|---|

| 0 | 0 | 通常のポートとしての動作。OC0B信号は非接続 |

| 0 | 1 | 予約 |

| 1 | 0 | OC0B端子をアップカウント動作中の比較一致でクリアし、ダウンカウント中の比較一致でセットする |

| 1 | 1 | OC0B端子をアップカウント動作中の比較一致でセットし、ダウンカウント中の比較一致でクリアする |

注意:1 OCR0BがTOP値と同じでCOM0B1がセットされている場合は、特殊なケース。この場合、比較一致は無視されるが、TOPでのセット、またはクリアは実行される。詳細は、「位相補正PWMモード」(p.96)を参照。

これらのビットはATmega48/88/168では将来拡張のため予約となっており、リード時は常にゼロになります。

TCCR0BレジスタのWGM02ビットと組み合わせて使用し、カウンターのカウント動作のシーケンス、最大値(TOP)にどの値を使用するか、どの種類の波形発生方法を使用するか、を制御します(Table14-8を参照)。このタイマー/カウンターでサポートされる動作モードは、通常モード、CTCモード、そして二種類のパルス幅変調(PWM)モードです(「動作モード」(p.93)を参照)。

Table 14-8. 波形発生モードビットの設定

| モード | WGM02 | WGM01 | WGM00 | 動作モード | TOP | OCRxの更新 | TOVフラグのセット |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | ノーマル | 0xFF | 即座に更新 | MAX |

| 1 | 0 | 0 | 1 | 位相補正PWM | 0xFF | TOP | BOTTOM |

| 2 | 0 | 1 | 0 | CTC | OCRA | 即座に更新 | MAX |

| 3 | 0 | 1 | 1 | 高速PWM | 0xFF | BOTTOM | MAX |

| 4 | 1 | 0 | 0 | 予約 | - | - | - |

| 5 | 1 | 0 | 1 | 位相補正PWM | OCRA | TOP | BOTTOM |

| 6 | 1 | 1 | 0 | 予約 | - | - | - |

| 7 | 1 | 1 | 1 | 高速PWM | OCRA | BOTTOM | TOP |

| 注意: MAX = 0xFF、BOTTOM = 0x00 |

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x25 (0x45) | FOC0A | FOC0B | - | - | WGM02 | CS02 | CS01 | CS00 | TCCR0B |

| Read/Write | W | W | R | R | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

FOC0AビットはWGMビットがPWM以外のモードに設定されている場合にのみ有効です。ただし、将来のデバイスとの互換性を保証するためには、PWMモードにおいてTCCR0Bに書き込みを行う際、このビットはゼロに設定しておかなければなりません。FOC0Aビットに論理値1を書き込むと、即座に波形発生ユニットでの比較一致動作が強制されます。

OC0A出力は、COM0A1:0ビットの設定に応じて変化します。FOC0Aビットはストローブ入力として実装されていることに注意してください。そのため、強制比較一致の動作結果は、COM0A1:0ビットにすでに設定されている値により決定されます。

FOC0Aによるストローブ動作では割り込みは発生せず、また、OCR0AをTOP値として動作しているCTCモードでのタイマークリアも行われません。

FOC0Aビットは、リード時には常にゼロです。

FOC0BビットはWGMビットがPWM以外のモードに設定されている場合にのみ有効です。ただし、将来のデバイスとの互換性を保証するためには、PWMモードにおいてTCCR0Bに書き込みを行う際、このビットはゼロに設定しておかなければなりません。FOC0Bビットに論理値1を書き込むと、即座に波形発生ユニットでの比較一致動作が強制されます。

OC0B出力は、COM0B1:0ビットの設定に応じて変化します。FOC0Bビットはストローブ入力として実装されていることに注意してください。そのため、強制比較一致の動作結果は、COM0B1:0ビットにすでに設定されている値により決定されます。

FOC0Bによるストローブ動作では割り込みは発生せず、また、OCR0BをTOP値として動作しているCTCモードでのタイマークリアも行われません。

FOC0Bビットは、リード時には常にゼロです。

これらのビットはATmega48/88/168では将来拡張のため予約となっており、リード時は常にゼロになります。

「TCCR0A - タイマー/カウンター・コントロール・レジスタ A」(p.100)の記載を参照してください。

3ビットのクロック選択ビットにより、タイマー/カウンターで使用されるクロックを選択します。

Table 14-9. クロック選択ビットの内容

| CS02 | CS01 | CS00 | 内容 |

|---|---|---|---|

| 0 | 0 | 0 | クロック源なし(タイマー/カウンター休止) |

| 0 | 0 | 1 | clkI/O (プリスケーラなし) |

| 0 | 1 | 0 | clkI/O / 8 (プリスケーラ出力) |

| 0 | 1 | 1 | clkI/O / 64 (プリスケーラ出力) |

| 1 | 0 | 0 | clkI/O / 256 (プリスケーラ出力) |

| 1 | 0 | 1 | clkI/O / 1024 (プリスケーラ出力) |

| 1 | 1 | 0 | T0端子の外部クロック源。ダウン・エッジ動作 |

| 1 | 1 | 1 | T0端子の外部クロック源。アップ・エッジ動作 |

タイマー/カウンター0が外部端子のクロックを使用するモードでは、T0端子が出力に設定されていたとしても、T0端子の状態変化によってカウンターが動作します。この機能により、ソフトウェアによってカウンターを動作させることが可能です。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x26 (0x46) | TCNT0[7:0] | TCNT0 | |||||||

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

タイマー/カウンター・レジスタによって、リード、ライトのどちらでも、タイマー/カウンターユニットの8ビット カウンターへの直接アクセスができます。TCNT0レジスタへの書き込みは、それに続く次のタイマークロックでの比較一致を無視(取り消し)します。カウント動作中にカウンター(TCNT0)の変更を行うと、TCNT0とOCR0xレジスタとの比較一致が正しく行われない可能性があります。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x27 (0x47) | OCR0A[7:0] | OCR0A | |||||||

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

比較レジスタAは、カウンターの値(TCNT0)と毎回比較される、8ビットの値を保持しています。比較一致によって、比較一致割り込みを発生させたり、OC0A端子に波形出力を発生させることができます。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x28 (0x48) | OCR0B[7:0] | OCR0B | |||||||

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

比較レジスタBは、カウンターの値(TCNT0)と毎回比較される、8ビットの値を保持しています。比較一致によって、比較一致割り込みを発生させたり、OC0B端子に波形出力を発生させることができます。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x6E) | - | - | - | - | - | OCIE0B | OCIE0A | TOIE0 | TIMSK0 |

| Read/Write | R | R | R | R | R | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

これらのビットはATmega48/88/168では将来拡張のため予約となっており、リード時は常にゼロになります。

OCIE0Bビットに1が書き込まれ、ステータスレジスタのIビットがセットされていると、タイマー/カウンターの比較一致B割り込みが有効になります。タイマー/カウンター割り込みフラグレジスタTIFR0のOCF0Bビットがセットされていれば、対応する割り込みがタイマー/カウンターの比較一致の際に実行されます。

OCIE0Aビットに1が書き込まれ、ステータスレジスタのIビットがセットされていると、タイマー/カウンターの比較一致A割り込みが有効になります。タイマー/カウンター割り込みフラグレジスタTIFR0のOCF0Aビットがセットされていれば、対応する割り込みがタイマー/カウンターの比較一致の際に実行されます。

TOIE0ビットに1が書き込まれ、ステータスレジスタのIビットがセットされていると、タイマー/カウンターのオーバーフロー割り込みが有効になります。 タイマー/カウンター割り込みフラグレジスタTIFR0のTOV0ビットがセットされていれば、対応する割り込みがタイマー/カウンターの比較一致の際に実行されます。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x15(0x35) | - | - | - | - | - | OCF0B | OCF0A | TOV0 | TIFR0 |

| Read/Write | R | R | R | R | R | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

これらのビットはATmega48/88/168では将来拡張のため予約となっており、リード時は常にゼロになります。

タイマー/カウンターと比較レジスタB(OCR0B)で比較一致が発生した際に、OCF0Bビットがセットされます。OCF0Bビットは対応する割り込み処理ベクターが実行されるときに、ハードウェアによってクリアされます。別の方法として、OCF0Bビットに論理値1を書き込むことで、クリアされます。ステータスレジスタのIビット、OCIE0Bビット(タイマー/カウンター比較一致B割り込みイネーブル)、およびOCF0Bビットがセットされている場合、タイマー/カウンター0 比較一致割り込みが発生します。

タイマー/カウンターと比較レジスタA(OCR0A)で比較一致が発生した際に、OCF0Aビットがセットされます。OCF0Aビットは対応する割り込み処理ベクターが実行されるときに、ハードウェアによってクリアされます。別の方法として、OCF0Aビットに論理値1を書き込むことで、クリアされます。ステータスレジスタのIビット、OCIE0Aビット(タイマー/カウンター比較一致A割り込みイネーブル)、およびOCF0Aビットがセットされている場合、タイマー/カウンター0 比較一致割り込みが発生します。

タイマー/カウンター0でオーバーフローが発生した際に、TOV0ビットがセットされます。TOV0ビットは対応する割り込み処理ベクターが実行されるときに、ハードウェアによってクリアされます。別の方法として、TOV0ビットに論理値1を書き込むことで、クリアされます。ステータスレジスタのIビット、TOIE0ビット(タイマー/カウンター・オーバーフロー割り込みイネーブル)、およびTOV0ビットがセットされている場合、タイマー/カウンター0 オーバーフロー割り込みが発生します。

このフラグの設定は、WGM02:0ビットの設定によって異なります。Table 14-8 「波形発生モードビットの設定」(p.102)を参照してください。