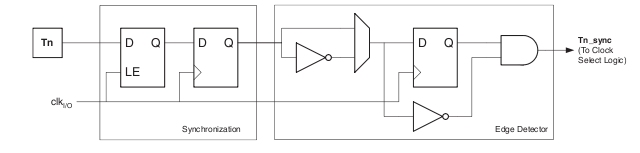

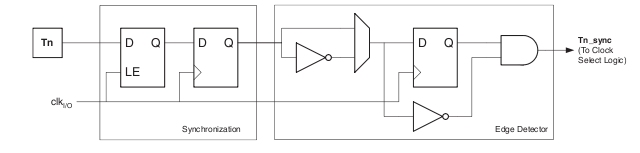

Figure 16-1. T1/T0 端子でのサンプリング

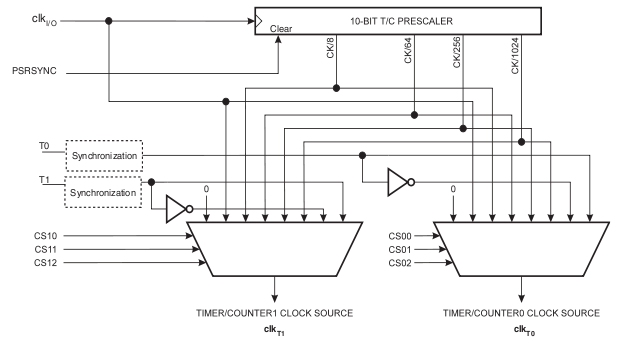

8ビット タイマー/カウンター0(p.88)と 16ビット タイマー/カウンター1(p.107)は、同一のプリスケーラ・モジュールを共有していますが、それぞれのタイマー/カウンター用に別々のプリスケーラ設定をすることができます。下記の説明は、タイマー/カウンター0とタイマー/カウンター1の両方に共通のものです。

タイマー/カウンターはシステム・クロックによって直接(CSn2:0 = 1の設定により)駆動することができます。この場合、最も高速な動作となり、タイマー/カウンターの最大クロック周波数は、システム・クロック周波数(fCLK_I/O)と同じになります。別の駆動方法として、プリスケーラの分周出力4つのうち一つをを使用してクロック源とすることができます。プリスケーラの分周クロックとして、fCLK_I/O/8, fCLK_I/O/64, fCLK_I/O/256, fCLK_I/O/1024のいずれかの周波数を選択することができます。

プリスケーラは他の信号により停止することなく動作し(たとえば、タイマー/カウンターのクロック選択ロジックと独立して動作)、タイマー/カウンター1とタイマー/カウンター0で共有されています。プリスケーラの動作がタイマー/カウンターのクロック選択に影響がないため、プリスケーラの状態により、分周クロックが使用される状況によっては問題が生じる可能性があります。一例として、タイマーが動作している状態で、そのクロックがプリスケーラにより分周されている((6 < CSn2:0 < 1))場合に、分周により生じるprescaling artifactがあります。タイマーが動作を開始してから、最初のカウント動作が行われるまでのシステム・クロック・サイクル数は、1から(N+1)システム・クロック・サイクルの間の値のいずれかとなります。ここでのNはプリスケーラの分周比(8, 64, 256, 1024)です。

プリスケーラのリセットを行えば、タイマー/カウンターをプログラムの実行に同期させることができます。ただし、もう一方のタイマー/カウンターが同一のプリスケーラを使って分周クロックを利用している場合は注意が必要です。プリスケーラのリセットは、それに接続されている全てのタイマー/カウンターの分周周期に影響を及ぼします。

外部のクロック源をT1/T0端子から入力して、タイマー/カウンターのクロック(clkT1/clkT0)として使用することができます。T1/T0端子の値は、システム・クロック・サイクルごとに端子の同期ロジック回路によりサンプリングされます。同期(サンプリング)された信号は、その後エッジ検出回路へと入力されます。Figure 16-1に、T1/T0の同期とエッジ検出回路の等価ブロック機能図を示します。各レジスタ(フリップ・フロップ)は内部のシステム・クロック(clkI/O)の正エッジでクロック動作します。ラッチ回路は、内部のシステム・クロックがHighの期間において透過状態となります。

エッジ検出回路により、各正エッジ(CSn2:0 = 7)または負エッジ(CSn2:0 = 6)ごとに、clkT1/T0が1パルス発生します。

同期およびエッジ検出回路により、エッジがT1/T0端子に入力されてから、カウンターが更新されるまでに、2.5から3.5システム・クロック・サイクルの遅延が生じます。

クロック入力の有効化または無効化は、T1/T0端子が少なくとも1システム・クロック・サイクルの期間安定している時に行う必要があり、そうでない場合は、タイマー/カウンターのクロックに異常なパルスが発生する可能性があります。

外部クロック入力の各半周期は、サンプリングが正しく動作するために、1システム・クロック・サイクルよりも長い必要があります。外部クロックは、システム・クロックの半分以下の周波数で(fExtClk < fclk_I/O / 2)、50%/50%のデューティー比である必要があります。エッジ検出回路がサンプリングを行っているため、検出できる外部クロックの最大周波数はサンプリング周波数の半分(ナイキストのサンプリング理論による)まで検出可能であるということです。ただし、発振回路(クリスタル、セラミック発振子、コンデンサ)の許容変動誤差から生じるシステム・クロック周波数とデューティー比の変動のため、外部クロック源の最大周波数は、fclk_I/O / 2.5以下であることが推奨されます。

外部クロック入力を分周することは出来ません。

注意:1. クロック入力端子(T1/T0)の同期回路は Figure 16-1 に描かれています。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x23 (0x43) | TSM | - | - | - | - | - | PSRASY | PSRSYNC | GTCCR |

| Read/Write | R/W | R | R | R | R | R | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

TSMビットに1を書き込むと、タイマー/カウンターの同期モードが有効になります。このモードでは、PSRASYビットとPSRSYNCビットに書き込まれた値は保持され、対象となるプリスケーラのリセット信号を発生し続けます。この機能により、対象となるタイマー/カウンターが全て停止して、設定中にカウント値を増加させることなく設定を行うことが出来ます。TSMビットにゼロが書き込まれると、PSRASYビットとPSRSYNCビットはハードウェアによりクリアされ、全てのタイマー/カウンターが同時にカウント動作を開始します。

このビットが1にセットされると、タイマー/カウンター1とタイマー/カウンター0のプリスケーラがリセットされます。このビットは、TSMビットがセットされている場合をのぞき、通常ハードウェアにより即座にクリアされます。タイマー/カウンター1とタイマー/カウンター0は同一のプリスケーラを共有しており、このプリスケーラをリセットすると両方のタイマーに影響があることにご注意ください。