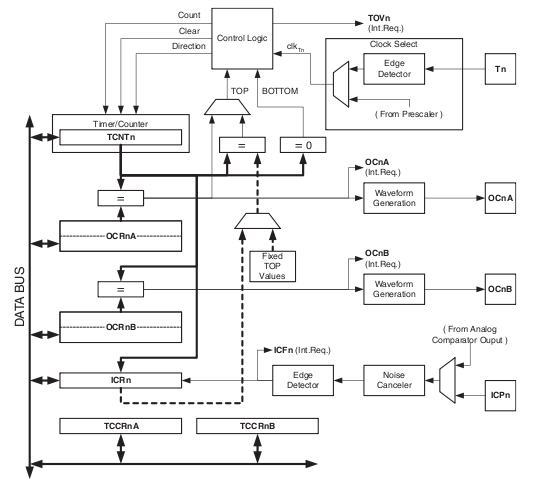

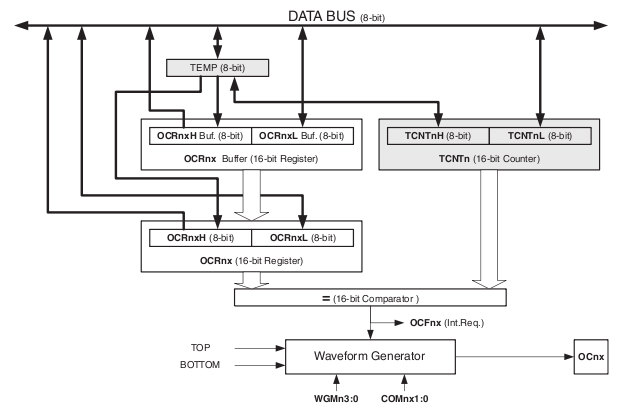

Figure 15-1. 16ビット タイマー/カウンター ブロック図

16ビットタイマー/カウンター・ユニットを利用することで、正確なプログラム実行タイミング(イベント管理)や波形発生が可能になります。

このセクションでは、多くのレジスタと各ビットの名称は一般化された形式で記されています。小文字の"n"は、タイマー/カウンターの番号、小文字の"x"は出力比較ユニットを表します。プログラム中で各レジスタやビットの定義を用いる場合は、正しい形式を使用しなければなりません。例えば、タイマー/カウンター1のカウント値にアクセスする場合はTCNT1を用いる、などです。

16ビット タイマー/カウンターの簡略ブロック図は Figure 15-1 をご覧ください。実際の入出力端子の配置については、「ピン接続図 ATmega48/88/168」(p.2)を参照してください。CPUがアクセス可能な入出力レジスタ、および各入出力ビット、入出力端子は太字で示されています。各デバイス固有の入出力レジスタとビットの配置は「レジスタ詳細」(p.129)を参照してください。

タイマー/カウンター1を有効にするためには、「PRR 消費電力低減レジスタ」(p.43)のPRTIM1 ビットに1を書き込んでおかなければなりません。

タイマー/カウンター(TCNT1)、出力比較レジスタ(OCR1A/B)およびインプット・キャプチャ・レジスタ(ICR1)は全て16ビットのレジスタです。16ビットのレジスタにアクセスする場合は、特別な手順にしたがって行う必要があります。これらの手順は「16ビットのレジスタにアクセスする」(p.109)の節で詳細を説明します。タイマー/カウンター・コントロール・レジスタ(TCCR1A/B)は8ビットのレジスタで、CPUのアクセスには特に制限はありません。割込み要求(図中では、Int.Req.と省略されています)信号は、タイマー割込みフラグ・レジスタ(TIFR1)で、いつでも読み取ることができます。割込みはすべてタイマー割込みマスク・レジスタ(TIMSK1)によって、個別に有効・無効の設定が可能です。TIFR1、およびTIMSK1レジスタはこの図中には描かれていません。

タイマー/カウンターはプリスケーラーを経由した内部クロックをカウントするか、T1端子に供給される外部クロックによってカウント動作を行います。クロック選択ブロックはどのクロック源、および、どのクロックエッジによって、タイマー/カウンターがアップ・カウント(またはダウン・カウント)動作をするかを制御します。タイマー/カウンターはクロック源が選択されていない場合は休止しています。クロック選択ブロックからの出力はタイマークロック(clkT1)という名称で呼びます。

二重バッファを備えた比較レジスタ (OCR1A/B) は、タイマー/カウンターの値と常に比較され、比較結果は波形発生器が比較一致出力端子 (OC1A/B) に、PWM出力や可変周波数出力を発生させるために使用されます。詳細については、「出力比較ユニット」(p.116)を参照してください。比較が一致した際には比較フラグ (OCF1A/B) がセットされ、比較一致割り込み要求を発生させるために使用されます。

インプット・キャプチャ・レジスタは、タイマー/カウンターの値を、インプット・キャプチャ端子(ICP1)、またはアナログ・コンパレータ端子(「アナログ・コンパレータ」(p.240)を参照)のいずれかを外部イベントとして指定でき、設定した外部イベントが発生した時(エッジによるトリガ動作)に取り込みます。インプット・キャプチャ部にはデジタル・フィルタ回路(ノイズ・キャンセラ)があり、スパイク状のノイズパルスをキャプチャしてしまう確率を低減します。

動作モードによっては、TOPの値(タイマー/カウンターの最大値)をOCR1Aレジスタ、ICR1レジスタのどちらか、または固定値の選択肢のなかから選んだ値を設定することができます。OCR1AをPWMモードでのTOP値として使用する場合、OCR1AレジスタはPWM出力を得るために利用することが出来ません。ただし、この場合TOP値は二重バッファ化されており、動作中にTOP値を変更することが可能になります。TOP値を固定値にする場合は、ICR1レジスタを代替として使用することができ、OCR1AレジスタをPWM出力用に使用することができるようになります。

下記の用語は、データシート中で頻繁に使用されます。

| BOTTOM | カウンターが0x0000になったときを、BOTTOMに達した、といいます。 |

| MAX | カウンターが0xFFFF(10進で65535)になったときを、MAXに達した、といいます。 |

| TOP | カウンターがカウント動作において最大値に達したときを、TOPに達したといいます。TOPの値は、固定値:0x00FF、0x01FF、0x03FFに設定するか、OCR1Aレジスタ、またはICR1レジスタの値に設定することが可能です。設定は動作モードによって異なります。 |

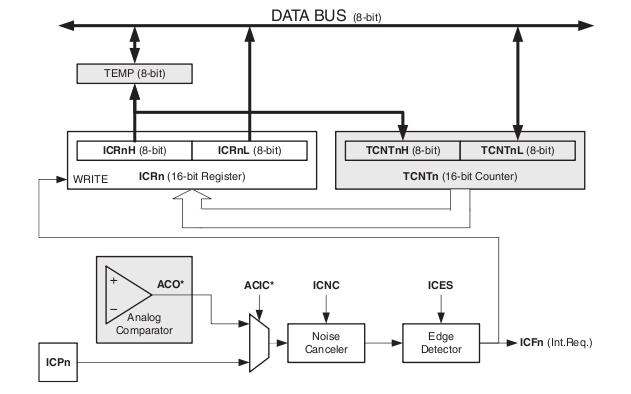

TCNT1、OCR1A/B、およびICR1は、AVR CPUからは8ビット幅のデータバスを通してアクセスされる、16ビットのレジスタです。16ビットのレジスタは二つのリードまたはライト動作によってアクセスしなければなりません。16ビットのタイマーには、単一の8ビットのレジスタが16ビットアクセスの際の上位バイトの一時的なデータ格納先レジスタとして備わっています。ひとつのタイマーの中では、この同一の一時データ用レジスタが全ての16ビットのレジスタで共有されています。下位バイトのリードまたはライト動作をトリガとして16ビット値のアクセスが動作します。16ビットの下位バイトがCPUによって書き込まれるときに、一時レジスタに保存された上位バイトと下位バイトが同時に、同一サイクルで16ビットの書き込み先レジスタに書き込まれます。16ビットの下位バイトがCPUによって読み出されるときに、下位バイトと同時に、同一サイクルで16ビットの上位バイトが一時レジスタにコピーされます。

必ずしも全ての16ビットのレジスタ・アクセスが、この上位バイトの一時レジスタを使用しているわけではありません。OCR1A/B 16ビットレジスタの読み取りには、この一時レジスタは使用されません。

16ビット値の書き込みを行うためには、上位バイトを下位バイトよりも先に書き込む必要があります。16ビット値の読み出しには、上位バイトよりも先に下位バイトを読み取る必要があります。

下記のコーディング例は、一時レジスタの内容を更新するような割込みが発生しないという前提で、16ビット タイマー・レジスタへのアクセス方法について示したものです。OCR1A/BおよびICR1レジスタへのアクセスについても、同様の考え方でアクセスすることができます。C言語では、16ビット値へのアクセス方法は、コンパイラが処理するという点にご注意ください。

| アセンブリ言語での例 |

... ; TCNT1 を 0x01FF にセットする ldi r17,0x01 ldi r16,0xFF out TCNT1H,r17 out TCNT1L,r16 ; TCNT1 の値を r17:r16 に読み取る in r16,TCNT1L in r17,TCNT1H ... |

| C言語での例 |

unsigned int i; ... /* TCNT1 を 0x01FF にセットする */ TCNT1 = 0x1FF; /* TCNT1 の値を i に読み取る */ i = TCNT1; ... |

注意: 「サンプル・コードについて」(p.7)を参照。 拡張I/Oマップ上の入出力レジスタでは、“IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, および “SBI”命令は、拡張I/Oにアクセスするための命令に置き換えなければなりません。典型的な例としては、“LDS”および “STS”命令を、 “SBRS”, “SBRC”, “SBR”, および“CBR”命令と組み合わせて使用します。

アセンブリ言語での例では、TCNT1の値をr17:r16レジスタ・ペアに格納してリターンしています。

16ビットのレジスタへのアクセスは、分割出来ない単一の処理であることに注意してください。16ビットのレジスタにアクセスしている二つの命令の間で割込みが発生し、その割込み処理中で同一または他の16ビットのタイマー・レジスタへのアクセスによって一時レジスタが更新されると、割込み処理外でのレジスタへのアクセスは異常な値となります。したがて、メイン処理、割込み処理の両方が一時レジスタを更新する場合、メイン処理側では、16ビットアクセスの際に割込みを禁止する必要があります。

次のコーディング例では、TCNT1レジスタの内容を単一の動作で読み取る方法を示しています。OCR1A/B、ICR1レジスタの読み取りも同様の考え方でアクセスすることが出来ます。

| アセンブリ言語での例 |

TIM16_ReadTCNT1: ; グローバル割込みフラグを保存 in r18,SREG ; 割込みを禁止 cli ; TCNT1 の値を r17:r16 に読み取る in r16,TCNT1L in r17,TCNT1H ; グローバル割込みフラグを元に戻す out SREG,r18 ret |

| C言語での例 |

unsigned int TIM16_ReadTCNT1( void )

{

unsigned char sreg;

unsigned int i;

/* グローバル割込みフラグを保存 */

sreg = SREG;

/* 割込みを禁止 */

_CLI();

/* TCNT1 の値を i に読み取る*/

i = TCNT1;

/* グローバル割込みフラグを元に戻す */

SREG = sreg;

return i;

}

|

注意: 「サンプル・コードについて」(p.7)を参照。 拡張I/Oマップ上の入出力レジスタでは、“IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, および “SBI”命令は、拡張I/Oにアクセスするための命令に置き換えなければなりません。典型的な例としては、“LDS”および “STS”命令を、 “SBRS”, “SBRC”, “SBR”, および“CBR”命令と組み合わせて使用します。

次のコーディング例では、単一の動作でTCNT1レジスタに書き込む方法を示しています。OCR1A/B、ICR1レジスタへの書き込みも同様の考え方で行うことが出来ます。

| アセンブリ言語での例 |

TIM16_WriteTCNT1: ; グローバル割込みフラグを保存 in r18,SREG ; 割込みを禁止 cli ; TCNT1 を r17:r16 の値に設定 out TCNT1H,r17 out TCNT1L,r16 ; グローバル割込みフラグを元に戻す out SREG,r18 ret |

| C言語での例 |

void TIM16_WriteTCNT1( unsigned int i )

{

unsigned char sreg;

unsigned int i;

/* グローバル割込みフラグを保存 */

sreg = SREG;

/* 割込みを禁止 */

_CLI();

/* TCNT1 を i の値に設定 */

TCNT1 = i;

/* グローバル割込みフラグを元に戻す */

SREG = sreg;

}

|

注意: 「サンプル・コードについて」(p.7)を参照。 拡張I/Oマップ上の入出力レジスタでは、“IN”, “OUT”, “SBIS”, “SBIC”, “CBI”, および “SBI”命令は、拡張I/Oにアクセスするための命令に置き換えなければなりません。典型的な例としては、“LDS”および “STS”命令を、 “SBRS”, “SBRC”, “SBR”, および“CBR”命令と組み合わせて使用します。

アセンブリ言語の例では、r17:r16レジスタペアにTCNT1に書き込む値が設定されている必要があります。

二つ以上の16ビットのレジスタに、上位バイトが同一の値を書き込む場合、上位バイトへは一度だけ書き込みを行えば十分です。ただし、この場合でも上述のように、分割されない単一処理として行う必要があることには変わりありません。

タイマー/カウンターは内部または外部のクロック源で動作します。クロック源の選択は、タイマー/カウンターコントロールレジスタ(TCCR1B)中のクロック選択ビット(CS12:0)によって制御されるクロック選択回路によって選択されます。クロック源とプリスケーラの詳細については、「タイマー/カウンター0、およびタイマー/カウンター1のプリスケーラ」(p.136)を参照してください。

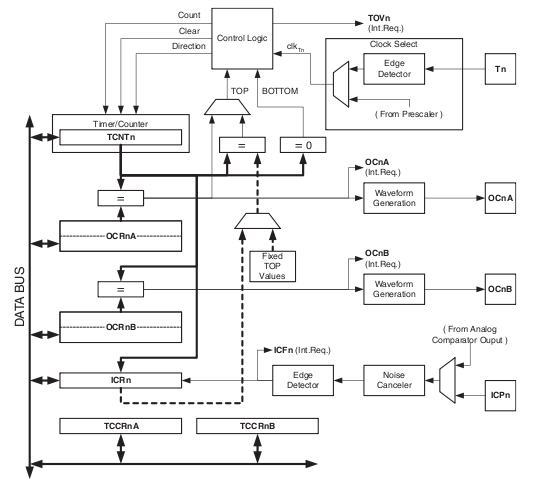

16ビット タイマー/カウンターの中心部はプログラマブル双方向カウンターユニットです。Figure 15-2 は、カウンターと周辺回路のブロック図です。

| Count | TCNT1 を1だけ、アップ・カウントまたはダウン・カウントする |

|---|---|

| Direction | アップ・カウント、ダウン・カウントの方向選択 |

| Clear | TCNT1 のクリア(全ビットを0にセット) |

| clkT1 | タイマー/カウンターのクロック。 |

| Top | TCNT1 が最大値に達した、という信号を発生 |

| Bottom | TCNT1 が最小値(0)に達した、という信号を発生 |

16ビット カウンターは、8ビットI/Oメモリ空間のアドレス二つに割り当てられています。カウンター上位バイト(TCNT1H)には上位8ビット、カウンター下位バイト(TCNT1L)には下位8ビットが含まれます。TCNT1Hレジスタは、CPUからは間接的な動作でのみアクセスされます。CPUがTCNT1HのI/Oアドレスにアクセスする場合、CPUは上位バイトの一時レジスタ(TEMP)にアクセスすることになります。この一時レジスタはTCNT1Lレジスタが読み出される時にTCNT1Hの値に更新され、TCNT1Lレジスタに書き込みが行われるときTCNT1Hは一時レジスタの値に更新されます。この動作により、8ビットのデータバスにおいて1クロック以内で16ビット カウンターの全内容を読み書きすることが出来ます。カウンターがカウント動作しているときにTCNT1レジスタへ書き込みを行う場合、予期できない動作結果をともなう特殊な場合が存在することに注意してください。この特殊な場合については、必要に応じて各節で記載します。

使用している動作モードに応じて、カウンターの値はクロック(clkT1)ごとに、クリア、インクリメント、またはデクリメントされます。clkT1は外部または内部のクロック源から生成され、クロック選択ビット(CS12:0)によって選択されます。クロックが選択されていない場合(CS12:0 = 0)、タイマーは停止しています。ただし、clkT1クロックの有無に関わらず、TCNT1の値はCPUからアクセス可能です。CPUによる書き込みは、すべてのカウンターのクリア、またはカウント動作を上書きします(CPUによる書き込みが優先されます)。

一連のカウント動作(カウント・シーケンス)は、タイマー/カウンター・コントロール・レジスタAおよびB(TCCR1AとTCCR1B)中のWGM13:0ビットによって決まります。カウンターのカウント動作と、比較ユニットのOC1x出力に発生する波形には密接な関係があります。カウント・シーケンスと波形発生についての、より高度な詳細は「動作モード」(p.119)をご覧ください。

タイマー/カウンター・オーバーフロー・フラグ (TOV1) は、WGM13:0 によって選択される動作モードに応じてセットされます。TOV1 フラグはCPUへの割り込みを発生するために使用できます。

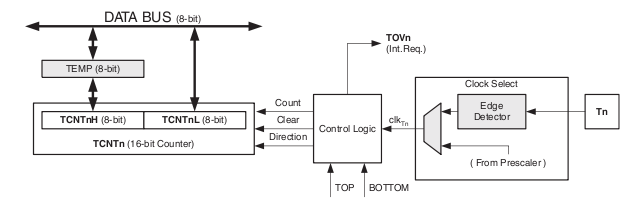

タイマー/カウンターには、インップト・キャプチャ・ユニットが実装されており、外部のイベントをキャプチャし、その発生時刻のタイムスタンプを得ることが出来ます。一つまたは複数のイベント発生を表す外部信号は、ICP1端子から入力するか、あるいは別の方法としてアナログ・コンパレータ・ユニットを通して入力することができます。タイムスタンプを用いて、入力信号の周波数、デューティー比、その他の特性を計算することが出来ます。また、タイムスタンプは、イベントのログ記録を作成するのにも使用できます。

インプット・キャプチャ・ユニットのブロック・ダイアグラムをFigure15-3に図示します。インプット・キャプチャ・ユニットに直接含まれない機能ブロックは灰色になっています。レジスタおよびビット名中の小文字の"n"は、タイマー/カウンターの番号を表しています。

インプット・キャプチャ入力端子(ICP1)に、または、アナログ・コンパレータ出力(AC0)に論理レベルの変化(イベント)が発生し、その変化がエッジ検出回路(Edge Detector)の設定に合致したものであるとき、キャプチャ信号が発生します。キャプチャ信号の発生をトリガーとして、カウンター(TCNT1)の16ビット値がインプット・キャプチャ・レジスタ(ICR1)に書き込まれます。TCNT1の値がICR1レジスタにコピーされるのと同一のシステムクロックで、インプット・キャプチャ・フラグ(ICF1)がセットされます。有効に設定されいる場合(ICIE1 = 1)に、インプット・キャプチャ・フラグによりインプット・キャプチャ割込みが発生します。ICF1フラグは割込みが処理されたときに自動的にクリアされます。別の方法として、ソフトウェアでICF1フラグのI/Oアドレスに論理値1を書き込むことによりクリアすることもできます。

インプット・キャプチャ・レジスタ(ICR1)の16ビット値の読み取りは、最初に下位バイト(ICR1L)を読み取り、その次に上位バイト(ICR1H)を読み取ることで行います。下位バイトが読み取られる時に、上位バイトが一時レジスタ(TEMP)にコピーされます。CPUがICR1HレジスタのI/Oアドレスに読み取り動作すると、TEMPレジスタの内容が読み出されます。

ICR1レジスタは、ICR1レジスタをカウンターのTOP値として指定する波形発生モードを使用しているときにのみ、書き込み可能です。この場合、TOP値をICR1レジスタに書き込むよりも前に、波形発生モード(WGM13:0)ビットを設定しておかなければなりません。ICR1レジスタに書き込みを行う場合は、上位バイトをICR1HのI/Oアドレスに書き込んでから、下位バイトをICR1Lに書き込む必要があります。

16ビットのレジスタにアクセスする方法についての詳細は、「16ビットのレジスタにアクセスする」(p.109)を参照してください。

インプット・キャプチャ・ユニットの主要なトリガ要因は、インプット・キャプチャ端子(ICP1)によるものです。これ以外に、タイマー/カウンター1では、アナログ・コンパレータの出力をインプット・キャプチャ・ユニットのトリガ要因として使用することが出来ます。アナログ・コンパレータ・コントロール/ステータス・レジスタ(ACSR)のアナログ・コンパレータ・インプット・キャプチャ(ACIC)ビットをセットすることで、アナログ・コンパレータをトリガ要因として選択することが出来ます。トリガ要因を変更することでトリガが発生する場合があることに注意してください。したがって、インプット・キャプチャ・フラグをトリガ設定変更後にクリアしなければなりません。

インプット・キャプチャ端子(ICP1)および、アナログ・コンパレータ出力(AC0)からの各入力はT1端子(Figure16-1 (p.136))と同様の回路を用いてサンプリングされています。エッジ検出回路も同じものが使われています。ただし、ノイズ・キャンセラが有効になっている場合、エッジ検出回路の前段に論理回路が追加され、システム・クロック4サイクル分、遅延が増加します。ノイズ・キャンセラとエッジ検出回路の入力は、タイマー/カウンターがICR1レジスタの値をTOP値として使用する波形発生モード以外では、常に有効になっている点にご注意ください。

インプット・キャプチャのトリガは、ソフトウェアによってICP1端子のポートをコントロールすることで発生させることが出来ます。

ノイズ・キャンセラを使用すると、デジタル・フィルタによりノイズ耐性を高めることができます。ノイズ・キャンセラの入力は、4回サンプリングを検査して、4つのサンプリング全てが同じになっている時にのみ出力を変化し、これをエッジ検出回路の入力として使用します。

タイマー/カウンター・コントロール・レジスタB(TCCR1B)のインプット・キャプチャ・ノイズ・キャンセラ(ICNC1)ビットをセットすると、ノイズ・キャンセラが有効になります。ノイズ・キャンセラを有効にすると、入力が変化してから、ICR1レジスタが更新するまでにシステム・クロック4サイクル分の遅延が追加で発生します。ノイズ・キャンセラはシステム・クロックを用いているので、プリスケーラによる影響はありません。

インプット・キャプチャ・ユニットを使う上で、入力されるイベント発生に対して十分なプロセッサ処理能力を割り当てできるかどうか、ということが重要な問題となります。二つのイベント発生間の時間が非常に重要です。次のイベント発生の前にICR1レジスタをプロセッサが読み取り完了していない場合でも、ICR1レジスタには新しい値が上書きされます。この場合、キャプチャ結果は正しくないものとなります。

インプット・キャプチャ・ユニットを使用する際には、割込み処理ルーチンの内部のできるだけ早い段階でICR1レジスタを読み取る必要があります。インプット・キャプチャ割込みは比較的高い優先度を与えられていますが、割込みの最大レスポンス・タイムは、他の割込み要求を処理するのに必要な最大クロック・サイクル数に依存します。

どのモードであっても、TOP値(カウンターの精度)を動作中に頻繁に変更するような使用方法で、インプット・キャプチャ・ユニットを使用することは推奨されません。

外部信号のデューティー比の測定には、キャプチャーの直後にトリガー・エッジの変更が必要になります。検出エッジの変更は、ICR1レジスタを読み取り完了してからできるだけ早く行う必要があります。エッジを変更した後、インプット・キャプチャ・フラグ(ICF1)をソフトウェアによってクリア(I/Oアドレスの該当ビットに論理値1を書き込む)する必要があります。周波数のみを測定する場合、ICF1フラグのクリアは必要ではありません(割込み処理ルーチンが使用されている場合)。

16ビットの比較一致検出回路によって、常に TCNT1 と比較レジスタ (OCR1x) の値が比較されます。TCNT1とOCR1xの値が一致したとき、一致検出回路は信号を発生します。一致検出信号によって、次のクロックサイクルで、一致フラグ (OCF1x) がセットされます。対応する割り込みが有効(OCIE1x = 1)になっている場合、一致フラグによって比較一致割り込みが発生します。割り込みが実行されると、OCF1xフラグは自動的にクリアされます。別の方法として、ソフトウェアによって、OC1Fxビットに論理値1を書き込むことで、一致フラグをクリアすることも可能です。波形発生器は比較一致信号を利用して、 WGM13:0 ビット、および比較一致出力モード・ビット(COM1x1:0)によって設定されている動作モードに応じた出力を発生させます。最大(TOP)および最小(BOTTOM)信号は、波形発生器が特定の動作モードで、タイマーの極大値・極小値での動作を決定するために利用されます(「動作モード」(p.119)を参照)。

出力比較ユニットAの特別な機能として、タイマー/カウンターのTOP値(例:カウンターの精度)として使用することができます。カウンターの精度決定のほか、TOP値は波形発生回路により生成される波形の周期を決定するのにも用いられます。

Figure 15-4に、出力比較ユニットのブロック図を示します。レジスタおよびビット名中の小文字の"n"は、デバイスの番号(n = 1の場合、タイマー/カウンター1)を表し、"x"は出力比較ユニット(A/B)を表します。出力比較ユニットに直接ふくまれない部分のブロックは灰色になっています。

PWMモードを使用している場合には、OCR1x レジスタは二重バッファが有効になっています。通常モードとクリア・タイマー・オン・コンペア(CTC)モードでは、二重バッファは無効になっています。二重バッファによって、OCR1x 比較レジスタの更新を、カウント・シーケンスの TOP値、またはBOTTOM値のいずれかに同期させて行います。この同期で、不揃いな長さの非対称なPWMパルスが発生することを防止し、出力に異常パルス(グリッチ)が現れなくなります。

この比較レジスタOCR1xへのアクセスは複雑に思えるかもしれませんが、そうではありません。二重バッファが有効になっていればCPUは比較レジスタのバッファにアクセスし、無効になっている場合、CPUは直接比較レジスタ OCR1xにアクセスするということです。OCR1x(比較レジスタ、またはバッファレジスタ)は、書き込み命令でのみ変更されます(TCNT1やICR1レジスタの用に、タイマー/カウンターがこのレジスタを自動的に更新することはありません)。したがって、OCR1xレジスタは上位バイトの一時レジスタ(TEMP)を通じての読み取り動作を行いません。しかし、他の16ビットのレジスタと同様に、読み取り時に下位バイトを先に読み取るようにするのは良い慣習であるといえます。OCR1xレジスタへの書き込みは、比較動作が継続して行われているため、一時レジスタを介して行わなければなりません。上位バイト(OCR1xH)への書き込みを先に行ってください。I/Oアドレスの上位バイトにCPUが書き込みを行うときに、TEMPレジスタがその書き込まれた値に更新されます。そして、下位バイト(OCR1xL)に下位8ビットを書き込むときに、上位バイトがOCR1xのバッファレジスタ、または比較レジスタの上位8ビットに、同一のシステムクロック・サイクルでコピーされます。

16ビットのレジスタにアクセスする方法の詳細については、「16ビットのレジスタにアクセスする」(p.109)を参照してください。

PWM波発生モードではない場合、強制一致ビット(FOC1x)に1を書き込むことにより、比較回路の一致出力を強制的に「一致したとする」ことができます。強制的に一致したとすることでは、比較一致フラグOCF1xはセットされず、またタイマーの再ロードやクリアも行われません。しかし、OC1x端子の状態は、実際に比較結果が一致したかのように更新されます(COM11:0 ビットの設定によって、OC1x 端子がセット、リセットまたは反転するのかが決まります)。

TCNT1レジスタへのCPUの書き込み動作は、どのような場合でも、その直後のタイマーのクロックサイクルで起きるはずの比較一致を阻止します。これはタイマーが停止している場合でも同じです。この機能により、タイマー/カウンターを有効にした途端に割り込みを発生させることなく、OCR1x レジスタを TCNT1 レジスタと同じ値に初期化することが可能になります。

TCNT1への書き込み動作によって、あらゆる比較一致が1タイマークロックサイクルの間無効になるため、比較ユニットを使用している状態でTCNT1の値を変更すると、タイマー/カウンターが動作しているかどうかに関係なく、問題が発生する可能性があります。もしTCNT1に書き込まれた値がOCR1xと同じ値であったとすると、(書き込みにより無効になっているため)比較一致が検出されず、結果として意図しない波形出力が発生します。TOP値の変更可能なPWMモードで動作している場合、TCNT1にTOP値と同じ値を書き込んではいけません。TOP値との比較一致は無視され、カウンターは0xFFFFまでカウント動作を継続します。同様に、ダウンカウント動作をしているカウンターでは、BOTTOM値と同じ値をTCNT1に書き込んではいけません。

OC1xの設定は、入出力方向レジスタに該当ポートの端子の出力設定を行う前に実行する必要があります。通常モードでOC1xの値を設定する一番簡単な方法は、強制一致ストローブ・ビット(FOC1x)を使用することです。これにより、OC1xレジスタの値は、波形発生モードを別のモードに変更する場合でも、正しく保持されます。

COM1x1:0 ビットは比較する値とは異なり、二重バッファになっていないことに注意してください。COM1x1:0 ビットへの変更は即座に動作に反映されます。

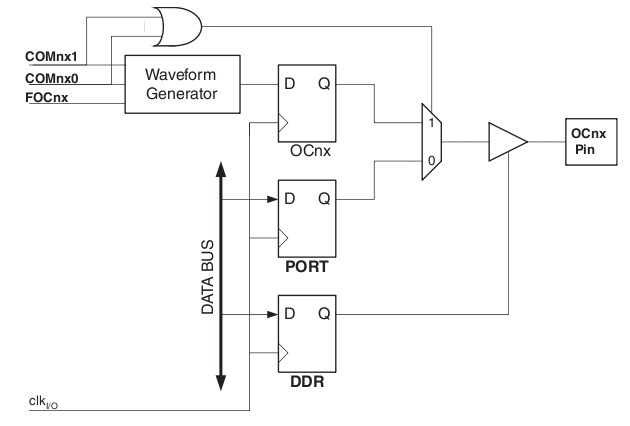

比較一致出力モードビット(COM1x1:0) には二つの機能があります。波形発生器はCOM1x1:0 ビットを使用して比較一致出力 (OC1x) の次回の比較一致時の状態を定義しています。また、COM1x1:0 ビットは OC1x出力端子にどの信号を出力するかの設定にも使用されます。Figure 15-5 に、COM1x1:0 ビットの設定によって影響を受ける論理回路の簡略化した回路図を示します。図中において、I/O レジスタ、I/O ビット、および I/O 入出力端子は太字で示されています。汎用I/Oポートのコントロールレジスタ(DDRおよびPORT)のうちCOM1x1:0 ビットによって影響を受けるもののみが描かれています。OC1x の状態を参照する際に対象となるのは、内部の OC1x ビット・レジスタであって、OC1x 端子の状態ではありません。システム・リセット時には OC1x ビット・レジスタはゼロにリセットされます。

汎用入出力ポートの機能は、COM1x1:0 ビットのいずれかがセットされている場合、波形発生器の比較出力(OC1x)の接続が優先されます。しかし、OC1x端子の入出力方向(設定が入力か、出力か)は、入出力方向レジスタ(DDR)によって対象となる端子の入出力方向が制御されています。入出力方向レジスタのOC1x端子(DDR_OC1x)の設定ビットは、OC1xの値が端子に反映されるよりも以前に、出力として設定されていなければなりません。ポートの端子機能の切り替えは、波形発生器のモードとは無関係ですが、いくつかの例外があります。詳細については、Table 15-1, Table 15-2, Table 15-3を参照してください。 。

この比較回路出力端子の設計によって、OC1xの状態を初期化してから出力を有効にすることが可能になります。COM1x1:0ビットの設定は特定の動作モードでは(将来拡張)予約となっていることに注意してください。詳しくは、「レジスタの詳細」(p.129)をご覧ください。

COM1x1:0ビットは、インプット・キャプチャ・ユニットの動作には影響しません。

波形発生器は、ノーマル、CTC、PWMモードの各モードで、COM1x1:0ビットを異なる意味に使っています。すべてのモードにおいて、COM1x1:0 = 0 は波形発生器に対して、OC1xレジスタが次回の比較一致の際に何もしない、という設定です。PWM以外のモードでの、比較一致の際のアクションについては、Table 15-1を参照してください。高速PWMモードについては、Table 15-2を、位相補正および位相周波数補正PWMモードについては、Table 15-3を参照してください。

COM1x1:0ビットの状態変更は、ビット書き込み後の最初の比較一致時の動作に影響があります。PWM以外のモードでは、FOC1xストローブ・ビットを使用することで、強制的に一致時のアクションを発生させることが可能です。

動作モード(例えば、タイマー/カウンターと比較一致出力端子の挙動)は、波形発生モード(WGM13:0ビット)と比較一致出力モード(COM1x1:0ビット)の組み合わせによって定義されます。比較一致出力モードビットの内容は、カウント・シーケンスに影響を与えません。カウント・シーケンスに影響があるのは、波形発生モードビットです。COM1x1:0ビットはPWM出力を反転出力(反転PWM波)とするか非反転出力(非反転PWM波)とするか、を設定します。PWM以外のモードでは、COM1x1:0ビットは出力をセットするか、クリアするか、または、反転(トグル)するかを設定します。(「比較一致出力ユニット」(p.118)を参照してください。)

動作タイミングの詳細な情報については、「タイマー/カウンター タイミング・ダイアグラム」(p.126)を参照してください。

通常モード(設定 WGM13:0 = 0)はもっとも単純な動作モードです。このモードでは、カウント動作の方向は常にアップカウント(インクリメント動作)で、カウンターのクリアは行われません。カウンターは16ビットの最大値(MAX = 0xFFFF)を単純に通過し、BOTTOM値(0x0000)から再度カウントを続けます。通常モードにおいて、タイマー/カウンター・オーバーフロー・フラグ(TOV1)はTCNT1がゼロになるのと同一のタイマー・クロック・サイクルにおいてセットされます。このとき、TOV1フラグは、セットのみされクリアされない、という点をのぞいて、17番目のビットのように振る舞います。しかし、タイマー・オーバーフロー割り込みと組み合わせ、TOV1フラグを自動的にクリアするようにすると、タイマーの精度をソフトウェアによって増加させることが可能です。通常モードにおいては、カウンターに新しい値をいつでも書き込み可能で、特別な状況を想定する必要はありません。

インプット・キャプチャ・ユニットは、簡単に通常モードで使用することができます。ただし、外部イベントの最大時間間隔がカウンターの精度を越えないように注意する必要があります。イベントの時間間隔が長すぎる場合、タイマー・オーバーフロー割込みや付リスケーラーを使用して、キャプチャ・ユニットを使用するのに適したカウント精度となるようにする必要があります。

比較出力ユニットを使用して、特定の時間で割り込みを発生させるように設定することが可能です。通常モードで、比較一致出力を波形発生のために使用することは推奨されません。なぜなら、それを実現するためには多くのCPU時間を必要とするからです。

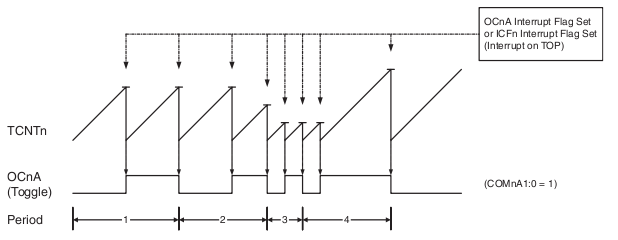

CTCモード (WGM13:0 = 4 または 12)では、OCR1Aレジスタ、またはICR1レジスタをカウンターの精度を操作するために使用します。CTCモードでは、カウンターはTCNT1の値がOCR1Aレジスタの値と等しくなった時(WGM13:0 = 4)、またはICR1の値と等しくなった時(WGM13:0 = 12)にクリアされます。OCR1Aレジスタ、またはICR1レジスタはカウンターの最大値を定義しており、したがって、その値がカウンターの精度となります。このモードを使用することで、比較一致出力の周波数を広範囲にわたって制御することが可能となります。また、外部イベントのカウント動作を簡単に行うこともできます。

CTCモードのタイミング・ダイアグラムはFigure 15-6に示されています。カウンターの値(TCNT1)はTCNT1とOCR1A、またはICR1との比較一致が発生するまで増加し、その後カウンター(TCNT1)がクリアされます。

TOP値を定義しているOCF1Aフラグ、またはICF1フラグを使用することで、カウンターの値が最大値(TOP)に達する度に、割り込みを発生させることが可能です。割り込みが有効になっていれば、割り込み処理ルーチン内で、最大値(TOP)の値設定を更新する、という使い方ができます。しかし、カウンターがプリスケーラなし、または、分周比の小さいプリスケーラで動作している時に、最大値(TOP)を最小値(BOTTOM)に近い値に更新するのには注意が必要です。なぜなら、CTCモードでは、二重バッファ機能は無効になっているためです。もし、OCR1AやICR1レジスタに新たに書き込まれた値が、その時点でのTCNT1の値よりも小さかったら、カウンターは比較一致に失敗することになります。その場合、カウンターは最大値(0xFFFF)までカウントして0x0000からスタートし、もう一周してから、比較一致が発生することになります。多くの場合、この動作は好ましいものではありません。別の適切な手段としては、OCR1AをTOP値として使用する高速PWMモード(WGM13:0 = 5)を使用して、OCR1Aレジスタが二重バッファ化されるようにすることです。

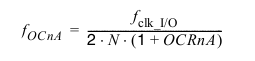

波形出力をCTCモードで使用するためには、比較一致出力モードビットをトグル・モード(COM1A1:0 = 1)に設定することで、OC1A出力が比較一致が起こる度に状態を反転(トグル)するように設定できます。OC1Aの値は、その端子の入出力方向が出力(DDR_OC1A = 1)に設定されていなければ、出力端子に反映されません。生成される波形は、OCR1Aがゼロ(0x0000)に設定されているとき、最大周波数 fOC1A = fclk_I/O/2 となります。波形の周波数は以下の式で計算されます。

Nの値はプリスケーラの分周比(1, 8, 64, 256, または 1024)を表します。

通常モードと同様に、TOV1フラグはカウンターのカウント値がMAX値から0x0000になるのと同じタイマー・クロック・サイクルでセットされます。

高速PWMモード(WGM13:0 = 5, 6, 7, 14, 15)では、高い周波数でのPWM波を発生させることが出来ます。高速PWMモードは、他のPWM動作モードとは、片方向カウントの動作である点が異なります。カウンターはBOTTOMからTOPまでカウントを行い、再びBOTTOMからカウントを再開します。比較一致が非反転出力モードのとき、比較一致出力(OC1x)はTCNT1とOCR1xの値が一致したときにクリアされ、BOTTOM値においてセットされます。反転出力モードでは、比較一致の時に出力がセットされ、BOTTOM値に達したときにクリアされます。 片方向カウント動作のため、高速PWMモードの動作周波数は双方向カウント動作である位相補正PWMモードや位相周波数補正PWMモードと比較して二倍の周波数にすることができます。このように高い動作周波数のため、高速PWMモードは電源の安定化、整流動作やD/Aコンバーターなどの応用に適しています。高い周波数での動作によって、外形寸法の小さな部品(コイル、コンデンサ)を用いることができ、したがってシステム全体のコストを削減することができます。

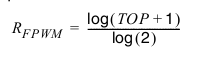

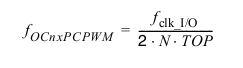

高速PWMモードでのPWMのカウント精度は、8、9、10ビットのいずれかに固定するか、ICR1またはOCR1Aレジスタにより設定することができます。設定可能な最小カウント精度は2ビット(ICR1またはOCR1Aを0x0003に設定)で、最大カウント精度は16ビット(ICR1またはOCR1AをMAX値に設定)です。PWMのカウント値のビット数は、次式で計算できます。

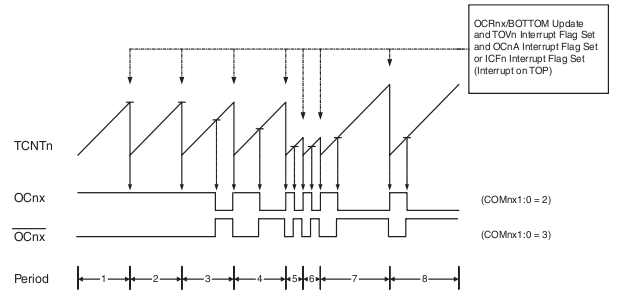

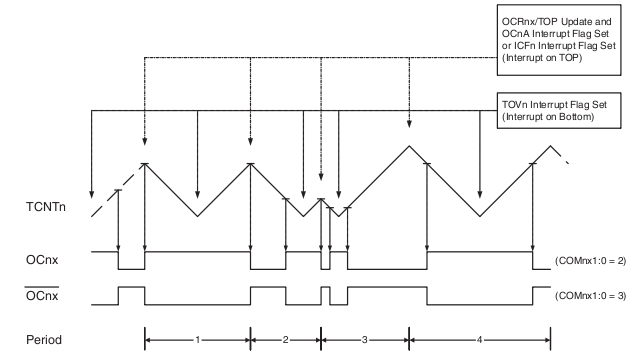

高速PWMモードでは、カウンターは値が0x00FF、0x01FF、0x03FF(WGM13:0 = 5, 6, or 7)、またはICR1 (WGM13:0 = 14)、OCR1A (WGM13:0 = 15)のいずれかと等しくなるまでインクリメントされ、そしてその次のタイマークロックサイクルでクリアされます。高速PWMモードのタイミング・ダイアグラムをFigure 15-7に示します。図では、OCR1AまたはICR1がTOP値として設定されている場合の高速PWMモードが示されています。ダイアグラム中では、TCNT1の値が片方向カウント動作であることを表すグラフになっていることがわかります。タイミング・ダイアグラムには、非反転および反転PWM出力もあわせて描かれています。小さな水平線で示されたTNT1の斜め線上の位置はOCR1xとTCNT1の値が一致したことを表しています。OC1x割込みフラグが比較一致が発生した際にセットされます。

タイマー/カウンター・オーバーフローフラグ(TOV1)は、カウンターがTOP値に到達すると毎回セットされます。さらに、OCR1AまたはICR1がTOP値の設定として使用されている場合、TOV1フラグがセットされるのと同一のタイマー・クロック・サイクルで、OC1AまたはICF1フラグもセットされます。いずれかの割り込みが有効になっていれば、割り込み処理ルーチン内でTOP値や比較対象のレジスタの値を更新することが可能です。

TOP値をソフトウェアで変更する際には、新しいTOP値が全ての比較対象のレジスタの値よりも大きいか等しい値であるようにしなければなりません。TOP値が比較対象のレジスタのいずれかよりも小さい値にすると、TCNT1とOCR1x間の比較一致がまったく発生しなくなります。なお、固定のTOP値を使用する際には、OCR1xレジスタのいずれかに書き込むとき、未使用ビットはゼロにマスクされます。

TOP値の設定として使用されている場合のICR1レジスタとOCR1Aレジスタでは、値の更新に必要な手順が異なります。ICR1レジスタは二重バッファ化されていません。このため、カウンターがプリスケーラなし、または小さな分周比で動作している状態でICR1が小さな値に変更されると、新しく書き込まれるICR1の値が、その時点でのTCNT1の値よりも小さくなる危険性があります。その結果、カウンターはTOP値での比較一致を正しくできないことになり、そのままMAX値(0xFFFF)までカウントをつづけ、0x0000から再スタートしてから比較一致を発生させることになります。 一方、OCR1Aレジスタは二重バッファ化されています。この機能により、OCR1AのI/Oアドレスには、いつでも書き込みを行うことが出来ます。OCR1AのI/Oアドレスに書き込みが行われると、書き込まれた値はOCR1Aのバッファ・レジスタに格納されます。その後、TCNT1がTOP値に一致したタイマー・クロック・サイクルの次のサイクルにおいて、OCR1A比較レジスタがバッファに格納されている値へと更新されます。この更新はTCNT1がクリアされ、TOV1フラグがセットされるのと同一のタイマー・クロック・サイクルにおいて行われます。

ICR1レジスタをTOP値の設定として使用する場合、固定のTOP値としての使用であれば、まったく問題は発生しません。ICR1レジスタを使用することで、PWM出力をOC1A端子に発生させる目的でOCR1Aレジスタを十分に活用することが出来ます。しかし、基本PWM周波数を頻繁に変更(TOP値を変更)するような使用法では、二重バッファ機能を備えたOCR1AレジスタをTOP値として使用する方が、明らかに良い選択といえます。

高速PWMモードでは、比較ユニットによってOC1x端子にPWM波出力を発生させることが出来ます。COM1x1:0ビットの設定を2にすることで非反転PWM出力を、COM1x1:0ビットの設定を3にすることで反転PWM出力を生成します(Table15-2 (p.129)を参照)。実際のOC1xの値がポートの出力端子に反映されるのは、該当端子の入出力方向の設定が出力設定(DDR_OC1x)になっている場合だけです。OCR1xとTCNT1の比較一致時にOC1xレジスタのセット(またはクリア)が行われ、カウンターがクリアされる(TOP値からBOTTOM値に更新)タイマークロックサイクルにおいて、OC1xレジスタがクリア(またはセット)されることによって、PWM波出力が発生します。

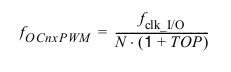

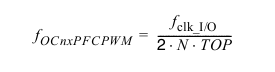

PWM波出力周波数は次式で計算できます。

Nの値はプリスケーラの分周比(1, 8, 64, 256, 1024)を表します。

PWM波出力を高速PWMモードで発生させているときに、OCR1xレジスタに極端な値を設定すると特殊な状態の出力となります。OCR1xレジスタがBOTTOM値(0x0000)と同じ値に設定されると、(TOP+1)タイマー・クロック・サイクルごとに短い幅のスパイク状のパルスが出力として現れます。OCR1xレジスタの値をTOP値と同じ値に設定すると、常にHiまたはLow(COM1x1:0 ビットによって設定された出力の極性により異なります)の出力となります。

高速PWMモードで可変周波数出力(50%デューティー比)を得るには、OC1Aレジスタの設定を比較一致のたびに、論理値をトグル(反転)するように設定(COM1A1:0 = 1)することで可能です。これは、OCR1AレジスタをTOP値として設定(WGM13:0 = 15)した場合にのみ使用可能です。この場合、出力の最大周波数は、OCR1Aがゼロ(0x0000)に設定されたときで、 fOC1A = fclk_I/O/2 となります。この機能は、高速PWMモードでは二重バッファが有効になっているという点以外は、CTCモードでのOC1Aのトグル(反転)動作と同様のものです。

位相補正PWMモード(WGM13:0 = 1, 2, 3, 10, 11)では、高精度の位相補正されたPWM波出力を可能にします。位相補正PWMモードは、位相周波数補正PWMモードと同じく、双方向カウントで動作します。カウンターはBOTTOM値(0x0000)からTOP値へ、そしてTOP値からBOTTOM値へと繰り返しカウントを行います。 非反転比較一致出力モードでは、一致出力(OC1x)は、アップカウント時ではTCNT1とOCR1xの比較一致時にクリアされ、ダウンカウント時でセットされます。反転一致出力モードでは、論理を反転した動作となります。双方向カウント動作は、片方向カウント動作とくらべて、最大周波数は低くなりますが、双方向カウントによるPWMモードの対称的な動作のため、このモードはモーターの制御に適しています。

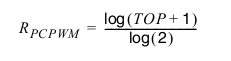

位相補正PWMモードでのPWMのカウント精度は、8、9、10ビットのいずれかに固定するか、ICR1またはOCR1Aレジスタにより設定することができます。設定可能な最小カウント精度は2ビット(ICR1またはOCR1Aを0x0003に設定)で、最大カウント精度は16ビット(ICR1またはOCR1AをMAX値に設定)です。PWMのカウント値のビット数は、次式で計算できます。

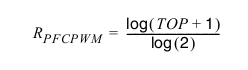

位相補正PWMモードでは、カウンターは値が0x00FF、0x01FF、0x03FF(WGM13:0 = 1, 2, 3)、またはICR1 (WGM13:0 = 10)、OCR1A (WGM13:0 = 11)のいずれかと等しくなるまでインクリメントされ、TOP値に達したとき、カウント方向を変更します。TCNT1の値は1タイマー・クロック・サイクルの期間、TOPの値と等しくなります。 位相補性PWMモードのタイミング・ダイアグラムをFigure 15-8に示します。図では、OCR1AまたはICR1がTOP値として設定されている場合の位相補性PWMモードが示されています。ダイアグラム中では、TCNT1の値が双方向カウント動作であることを表すグラフになっていることがわかります。タイミング・ダイアグラムには、非反転および反転PWM出力もあわせて描かれています。小さな水平線で示されたTNT1の斜め線上の位置はOCR1xとTCNT1の値が一致したことを表しています。OC1x割込みフラグが比較一致が発生した際にセットされます。

タイマー/カウンター・オーバーフローフラグ(TOV1)は、カウンターがTOP値に到達すると毎回セットされます。 さらに、OCR1AまたはICR1がTOP値の設定として使用されている場合、OCR1xレジスタが二重バッファにより(TOP値において)更新されるのと同一のタイマー・クロック・サイクルで、OC1AまたはICF1フラグがセットされます。いずれかの割り込みが有効になっていれば、カウンターがTOP値またはBOTTOM値に達する度に割込みを発生させることができます。

TOP値をソフトウェアで変更する際には、新しいTOP値が全ての比較対象のレジスタの値よりも大きいか等しい値であるようにしなければなりません。TOP値が比較対象のレジスタのいずれかよりも小さい値にすると、TCNT1とOCR1x間の比較一致がまったく発生しなくなります。なお、固定のTOP値を使用する際には、OCR1xレジスタのいずれかに書き込むとき、未使用ビットはゼロにマスクされます。 Figure15-8に描かれている第3周期のように、位相補正PWMモードで動作しているタイマー/カウンターのTOP値を積極的に変更するような使用法では、非対称の出力を生じる可能性があります。この原因はOCR1xレジスタの更新タイミングにあります。OCR1xレジスタの更新はTOP値において行われるため、PWM周期はTOP値において開始および終了します。このことは、右下がりの期間が更新前の周期のTOP値によって決まり、右上がりの期間が更新後のTOP値によって決まることを意味します。この二つの値が異なっていると、その周期の上り下りの両期間が異なってしまいます。この期間の相違により非対称な出力が生じます。

タイマー/カウンター動作中にTOP値を変更する使用法では、位相補正モードではなく、位相周波数補正モードの使用が推奨されます。固定のTOP値を使用する場合、二つの動作モードには実用上の違いはありません。

位相補正PWMモードでは、比較ユニットによってOC1x端子にPWM波出力を発生させることが出来ます。COM1x1:0ビットの設定を2にすることで非反転PWM出力を、COM1x1:0ビットの設定を3にすることで反転PWM出力を生成します(Table15-3 (p.130)を参照)。実際のOC1xの値が出力端子に反映されるのは、該当端子の入出力方向の設定が出力設定(DDR_OC1x)になっている場合だけです。OCR1xとTCNT1のアップカウントでの比較一致時にOC1xレジスタのセット(またはクリア)が行われ、OCR1xとTCNT1のダウンカウントでの比較一致時にOC1xレジスタのカウンターがクリア(またはセット)されることによって、PWM波出力が発生します。位相補正PWMモードでのPWM周波数は次式により計算できます。

Nの値はプリスケーラの分周比(1, 8, 64, 256, 1024)を表します。

PWM波出力を位相補正PWMモードで発生させているときに、OCR1xレジスタに極端な値を設定すると特殊な状態の出力となります。非反転出力モードでは、OCR1xレジスタがBOTTOM値と同じ値に設定されると、出力は常にLowとなり、MAX値と同じ値に設定すると常にHiとなります。反転出力モードでは、論理値を逆転した出力になります。OCR1AレジスタがTOP値として設定(WGM13:0 = 11)されていて、COM1A1:0 = 1の場合、OC1A出力は50%デューティー比で極性を反転する出力となります。

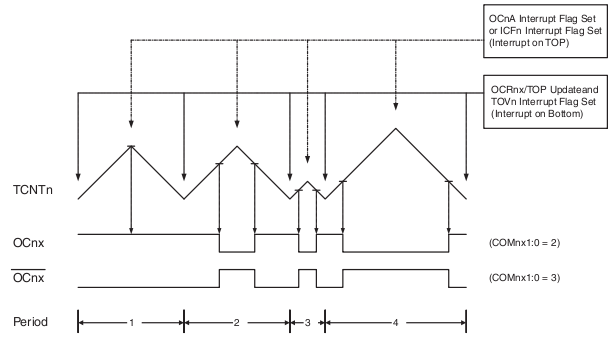

位相周波数補正PWMモード(WGM13:0 = 8、または9)では、位相と周波数が補正された高精度のPWM波出力を可能にします。位相周波数補正PWMモードは、位相補正PWMモードと同じく、双方向カウントで動作します。カウンターはBOTTOM値(0x0000)からTOP値へ、そしてTOP値からBOTTOM値へと繰り返しカウントを行います。 非反転比較一致出力モードでは、一致出力(OC1x)は、アップカウント時ではTCNT1とOCR1xの比較一致時にクリアされ、ダウンカウント時でセットされます。反転一致出力モードでは、論理を反転した動作となります。双方向カウント動作は、片方向カウント動作とくらべて、最大周波数は低くなりますが、双方向カウントによるPWMモードの対称的な動作のため、このモードはモーターの制御に適しています。

位相補正PWMモードと位相周波数補正PWMモードの主なちがいは、OCR1xレジスタがOCR1xバッファ・レジスタにより更新されるタイミングにあります(Figure 15-8とFigure15-9を参照)。

位相補正PWMモードでのPWMのカウント精度は、ICR1レジスタ、またはOCR1Aレジスタにより設定することができます。設定可能な最小カウント精度は2ビット(ICR1またはOCR1Aを0x0003に設定)で、最大カウント精度は16ビット(ICR1またはOCR1AをMAX値に設定)です。PWMのカウント値のビット数は、次式で計算できます。

位相周波数補正PWMモードでは、カウンターは値がICR1 (WGM13:0 = 8)、またはOCR1A (WGM13:0 = 9)のいずれかと等しくなるまでインクリメントされ、TOP値に達したとき、カウント方向を変更します。TCNT1の値は1タイマー・クロック・サイクルの期間、TOPの値と等しくなります。 位相周波数補性PWMモードのタイミング・ダイアグラムをFigure 15-9に示します。図では、OCR1AまたはICR1がTOP値として設定されている場合の位相周波数補性PWMモードが示されています。ダイアグラム中では、TCNT1の値が双方向カウント動作であることを表すグラフになっていることがわかります。タイミング・ダイアグラムには、非反転および反転PWM出力もあわせて描かれています。小さな水平線で示されたTNT1の斜め線上の位置はOCR1xとTCNT1の値が一致したことを表しています。OC1x割込みフラグが比較一致が発生した際にセットされます。

タイマー/カウンター・オーバーフローフラグ(TOV1)は、OCR1xレジスタが二重バッファにより(BOTTOM値において)更新されるのと同一のタイマー・クロック・サイクルで、セットされます。OCR1AまたはICR1がTOP値の設定として使用されている場合、OC1AまたはICF1フラグがTOP値においてセットされます。その際に割込みフラグを使用して、カウンターがTOP値またはBOTTOM値に達する度に割込みを発生させることが出来ます。

TOP値をソフトウェアで変更する際には、新しいTOP値が全ての比較対象のレジスタの値よりも大きいか等しい値であるようにしなければなりません。TOP値が比較対象のレジスタのいずれかよりも小さい値にすると、TCNT1とOCR1x間の比較一致がまったく発生しなくなります。

Figure15-9に描かれているように、生成される出力は位相補正モードとは異なり、すべての周期において対称となっています。OCR1xレジスタはBOTTOM値において更新されるため、右上がりの期間と右下がりの期間は常に等しくなります。これにより、対称な出力パルスを生成し、正確な周波数出力を可能にします。

ICR1レジスタをTOP値の設定として使用する場合、固定のTOP値としての使用であれば、まったく問題は発生しません。ICR1レジスタを使用することで、PWM出力をOC1A端子に発生させる目的でOCR1Aレジスタを十分に活用することが出来ます。しかし、基本PWM周波数を頻繁に変更(TOP値を変更)するような使用法では、二重バッファ機能を備えたOCR1AレジスタをTOP値として使用する方が、明らかに良い選択といえます。

位相周波数補正PWMモードでは、比較ユニットによってOC1x端子にPWM波出力を発生させることが出来ます。COM1x1:0ビットの設定を2にすることで非反転PWM出力を、COM1x1:0ビットの設定を3にすることで反転PWM出力を生成します(Table15-3 (p.130)を参照)。実際のOC1xの値が出力端子に反映されるのは、該当端子の入出力方向の設定が出力設定(DDR_OC1x)になっている場合だけです。OCR1xとTCNT1のアップカウントでの比較一致時にOC1xレジスタのセット(またはクリア)が行われ、OCR1xとTCNT1のダウンカウントでの比較一致時にOC1xレジスタのカウンターがクリア(またはセット)されることによって、PWM波出力が発生します。位相周波数補正PWMモードでのPWM周波数は次式により計算できます。

Nの値はプリスケーラの分周比(1, 8, 64, 256, 1024)を表します。

PWM波出力を位相周波数補正PWMモードで発生させているときに、OCR1xレジスタに極端な値を設定すると特殊な状態の出力となります。非反転出力モードでは、OCR1xレジスタがBOTTOM値と同じ値に設定されると、出力は常にLowとなり、MAX値と同じ値に設定すると常にHiとなります。反転出力モードでは、論理値を逆転した出力になります。OCR1AレジスタがTOP値として設定(WGM13:0 = 9)されていて、COM1A1:0 = 1の場合、OC1A出力は50%デューティー比で極性を反転する出力となります。

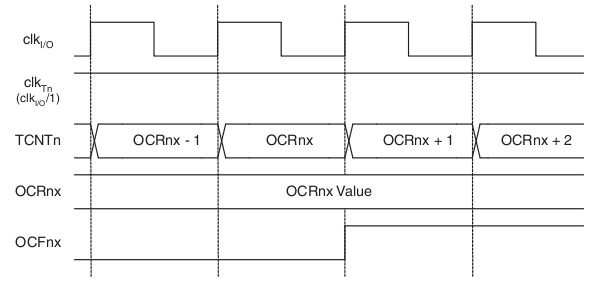

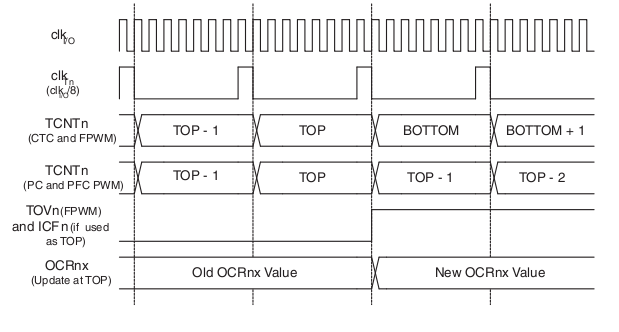

タイマー/カウンターは同期カウンタであるため、タイマークロック(clkT1)は以下の図においてクロック・イネーブル信号として示されています。各図は割り込みフラグがいつセットされるのか、そしてOCR1xレジスタがOCR1xバッファでいつ更新されるのか(二重バッファを使用するモードのみ)、ということをあわせて描かれています。Figure 15-10は、OCF1xフラグのセットされるタイミングを表しています。

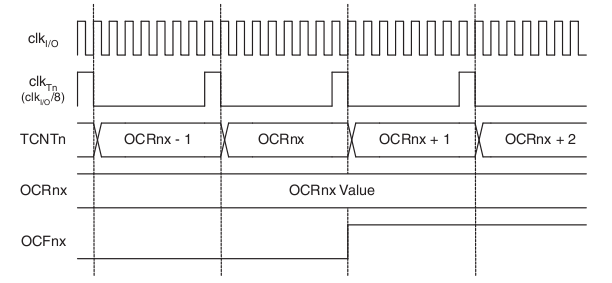

Figure 15-11 はプリスケーラが有効になっている点以外は、同じタイミング・データを示しています。

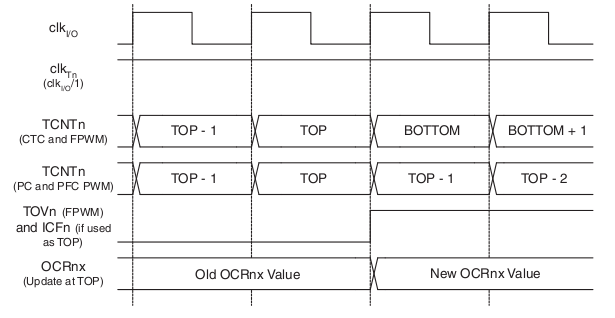

Figure 15-12では、様々なモードでのカウント・シーケンスについて描かれています。位相周波数補正PWMモードでは、OCR1xレジスタがBOTTOMにおいて更新されます。タイミング・ダイアグラムは同じですが、TOPをBOTTOMに、TOP-1をBOTTOM+1に、というように置き換えてください。同様の名称変更はBOTTOMにおいてTOV1フラグをセットするモードについてもあてはまります。

Figure 15-13 はプリスケーラが有効になっている点以外は、同じタイミング・データを示しています。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x80) | COM1A1 | COM1A0 | COM1B1 | COM1B0 | - | - | WGM11 | WGM10 | TCCR1A |

| Read/Write | R/W | R/W | R/W | R/W | R | R | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

COM1A1:0、およびCOM1B1:0ビットは比較一致出力端子(それぞれOC1A、およびOC1B)の動作を制御します。一つ、または二つのCOM1A1:0ビットがセットされると、OC1A出力が優先され、接続されている入出力端子の通常のI/Oポート機能は無効になります。一つ、または二つのCOM1B1:0ビットがセットされると、OC1B出力が優先され、接続されている入出力端子の通常のI/Oポート機能は無効になります。ただし、データ方向レジスタ(DDR)のOC1A、OC1B端子に対応するビットは、出力が有効になるように設定されていなければなりません。

OC1A出力、またはOC1B出力が端子に接続されている場合、COM1x1:0ビットの機能は、WGM13:0ビットの設定によって変わります。Table 15-1に、WGM13:0ビットが通常モード、またはCTCモード(つまりPWM以外のモード)に設定されている場合の、COM0A1:0ビットの機能を示します。

Table 15-1. 比較一致出力のモード (PWMモード以外)

| COM1A1/COM1B1 | COM1A0/COM1B0 | 内容 |

|---|---|---|

| 0 | 0 | 通常のポートとしての動作。OC1A/OC1B出力は非接続 |

| 0 | 1 | OC1A/OC1B端子を比較一致の際にトグル(反転) |

| 1 | 0 | OC1A/OC1B端子を比較一致の際にクリア(出力をLowにする) |

| 1 | 1 | OC1A/OC1B端子を比較一致の際にセット(出力をHiにする) |

Table 15-2に、WGM13:0ビットが高速PWMモードに設定されている場合の、COM1x1:0ビットの機能を示します。

Table 15-2. 比較一致出力のモード (高速PWMモード)

| COM1A1/COM1B1 | COM1A0/COM1B0 | 内容 |

|---|---|---|

| 0 | 0 | 通常のポートとしての動作。OC1A/OC1B出力は非接続 |

| 0 | 1 |

WGM13:0 = 14, 15: OC1A出力を比較一致において反転(トグル)する。 OC1B出力は非接続(通常のポート動作)。

他のWGM1設定では、すべて通常のポート動作をおこない、OC1A/OC1B出力は非接続。 |

| 1 | 0 | OC1A/OC1B出力を比較一致の際にクリアし、BOTTOM値においてOC1A/OC1B出力をセット(非反転モード) |

| 1 | 1 | OC1A/OC1B出力を比較一致の際にセットし、BOTTOM値においてOC1A/OC1B出力をクリア(反転モード) |

注意:1 OCR1A/OCR1BがTOP値と同じで、COM1A1/COM1B1がセットされている場合は、特殊なケース。この場合、比較一致は無視されるが、BOTTOMでのセット、またはクリアは実行される。詳細は、「高速PWMモード」(p.120)を参照。

Table 15-3に、WGM13:0ビットが位相補正PWMモード、または位相周波数補正PWMモードに設定されている場合の、COM1x1:0ビットの機能を示します

Table 15-3. 比較一致出力のモード (位相補正、および位相周波数補正PWMモード)

| COM1A1/COM1B1 | COM1A0/COM1B0 | 内容 |

|---|---|---|

| 0 | 0 | 通常のポートとしての動作。OC1A/OC1B出力は非接続 |

| 0 | 1 |

WGM13:0 = 9、11: OC1A出力を比較一致において反転(トグル)する。 OC1B出力は非接続(通常のポート動作)。

他のWGM1設定では、すべて通常のポート動作をおこない、OC1A/OC1B出力は非接続。 |

| 1 | 0 | アップカウント動作中の比較一致の際にOC1A/OC1B出力をクリア。ダウンカウント動作中の比較一致の際にOC1A/OC1B出力をセット |

| 1 | 1 | アップカウント動作中の比較一致の際にOC1A/OC1B出力をセット。ダウンカウント動作中の比較一致の際にOC1A/OC1B出力をクリア |

注意:1 OCR1A/OCR1BがTOP値と同じでCOM1A1/COM1B1がセットされている場合は、特殊なケース。詳細は、「位相補正PWMモード」(p.122)を参照。

TCCR1BレジスタのWGM13:2ビットと組み合わせて使用し、カウンターのカウント動作のシーケンス、最大値(TOP)にどの値を使用するか、どの種類の波形発生方法を使用するか、を制御します(Table15-4を参照)。このタイマー/カウンターでサポートされる動作モードは、通常モード、CTC モード、そして三種類のパルス幅変調(PWM)モードです(「動作モード」(p.119)を参照)。

Table 15-4.

波形発生モードビットの内容

| モード | WGM13 |

WGM12 (CTC1) |

WGM11 (PWM11) |

WGM10 (PWM10) |

動作モード | TOP値 | OCR1xの更新 | TOV1フラグのセット |

|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 通常 | 0xFFFF | 即時更新 | MAX |

| 1 | 0 | 0 | 0 | 1 | 位相補正PWM、8ビット | 0x00FF | TOP | BOTTOM |

| 2 | 0 | 0 | 1 | 0 | 位相補正PWM、9ビット | 0x01FF | TOP | BOTTOM |

| 3 | 0 | 0 | 1 | 1 | 位相補正PWM、10ビット | 0x03FF | TOP | BOTTOM |

| 4 | 0 | 1 | 0 | 0 | CTC | OCR1A | 即時更新 | MAX |

| 5 | 0 | 1 | 0 | 1 | 高速PWM、8ビット | 0x00FF | BOTTOM | TOP |

| 6 | 0 | 1 | 1 | 0 | 高速PWM、9ビット | 0x01FF | BOTTOM | TOP |

| 7 | 0 | 1 | 1 | 1 | 高速PWM、10ビット | 0x03FF | BOTTOM | TOP |

| 8 | 1 | 0 | 0 | 0 | 位相周波数補正PWM | ICR1 | BOTTOM | BOTTOM |

| 9 | 1 | 0 | 0 | 1 | 位相周波数補正PWM | OCR1A | BOTTOM | BOTTOM |

| 10 | 1 | 0 | 1 | 0 | 位相補正PWM | ICR1 | TOP | BOTTOM |

| 11 | 1 | 0 | 1 | 1 | 位相補正PWM | OCR1A | TOP | BOTTOM |

| 12 | 1 | 1 | 0 | 0 | CTC | ICR1 | 即時更新 | MAX |

| 13 | 1 | 1 | 0 | 1 | (予約) | - | - | - |

| 14 | 1 | 1 | 1 | 0 | 高速PWM | ICR1 | BOTTOM | TOP |

| 15 | 1 | 1 | 1 | 1 | 高速PWM | OCR1A | BOTTOM | TOP |

1. CTC1、PWM11:0 ビットの定義名は現在は使用しなし旧名称です。新しい定義名であるWGM12:0を使用してください。ただし、これらのビットのアドレス位置と機能については、旧バージョンのタイマーモジュールと互換性があります。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x81) | ICNC1 | ICES1 | - | WGM13 | WGM12 | CS12 | CS11 | CS10 | TCCR1B |

| Read/Write | R/W | R/W | R | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

このビットをセット(1)にすると、インプット・キャプチャ・ノイズ・キャンセラが有効になります。ノイズ・キャンセラが動作している場合、インプット・キャプチャ端子(ICP1)からの入力はフィルターを通ります。ICP1端子のサンプリング値が4つの連続して全て等しい場合にのみ、出力を変化させるのがフィルターの機能です。したがって、ノイズ・キャンセラが有効になっている場合、インプット・キャプチャ入力では4サイクルの遅延が発生します。

このビットにより、インプット・キャプチャ端子(ICP1)によりキャプチャ・イベントを発生させる際に用いる動作エッジを選択します。ICES1ビットがゼロの場合、立ち下がり(ネガティブ)エッジがトリガーに使用され、ICES1ビットが1の場合、立ち上がり(ポジティブ)エッジがトリガーに使用され、キャプチャを行います。

ICES1の設定にしたがってキャプチャがトリガーされると、カウンターの値がインプット・キャプチャ・レジスタ (ICR1)にコピーされます。また、このキャプチャ・イベントにより、インプット・キャプチャ・フラグ(ICF1)がセットされ、割込みが有効になっている場合にインプット・キャプチャ割込みを発生させるのに使用することが出来ます。

ICR1レジスタがTOP値として使用されている場合(TCCR1A、TCCR1Bレジスタ中のwGM13:0ビットの説明を参照)、ICP1は非接続となり、それにともない、インプット・キャプチャ機能は無効になります。

このビットは将来拡張のため予約となっています。将来デバイスとの互換性を確保するために、TCCR1Bレジスタに書き込みを行う場合はゼロを書き込んでください。

TCCR1Aレジスタの説明を参照。

3ビットのクロック選択ビットにより、タイマー/カウンターで使用されるクロックに何を使うかを選択します。Figure 15-10、および Figure 15-11を参照してください。

Table 15-5.

クロック選択ビットの内容

| CS12 | CS11 | CS10 | 内容 |

|---|---|---|---|

| 0 | 0 | 0 | クロック源なし(タイマー/カウンター休止) | 0 | 0 | 1 | clkI/O / 1 (プリスケーラなし) | 0 | 1 | 0 | clkI/O / 8 (プリスケーラ出力) | 0 | 1 | 1 | clkI/O / 64 (プリスケーラ出力) | 1 | 0 | 0 | clkI/O / 256 (プリスケーラ出力) | 1 | 0 | 1 | clkI/O / 1024 (プリスケーラ出力) | 1 | 1 | 0 | T1端子の外部クロック源。ダウン・エッジ動作 | 1 | 1 | 1 | T1端子の外部クロック源。アップ・エッジ動作 |

タイマー/カウンター1が外部端子のクロックを使用するモードでは、T1端子が出力に設定されていたとしても、T1端子の状態変化によってカウンターが動作します。この機能により、ソフトウェアによってカウンターを動作させることが可能です。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x82) | FOC1A | FOC1B | - | - | - | - | - | - | TCCR1C |

| Read/Write | R/W | R/W | R | R | R | R | R | R | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

FOC1A/FOC1BビットはWGM13:0ビットがPWM以外のモードに設定されている場合にのみ有効です。FOC1A/FOC1Bビットに論理値1を書き込むと、即座に波形発生ユニットでの比較一致動作が強制されます。OC1A/OC1B出力は、COM1x1:0ビットの設定にしたがって変化します。FOC1A/FOC1Bビットはストローブ入力として実装されていることに注意してください。そのため、強制比較一致の動作結果は、COM1x1:0ビットにすでに設定されている値により決定されます。

FOC1A/FOC1Bによるストローブ動作では割り込みは発生せず、また、OCR1AをTOP値として動作しているCTCモードでのタイマーのクリアも行われません。

FOC1A/FOC1Bビットは、リード時には常にゼロです。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x85) | TCNT1[15:8] | TCNT1H | |||||||

| (0x84) | TCNT1[7:0] | TCNT1L | |||||||

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

タイマー/カウンター・レジスタの二つのI/Oアドレス(TCNT1H、TCNT1L、あわせてTCNT1)を通して、タイマー/カウンター・ユニットの16ビット・カウンターに直接リード/ライトを行うことが出来ます。CPUがこれらのレジスタにアクセスする際に、確実に上位バイトと下位バイトが同時に読み書きできるように、このレジスタへのアクセスは8ビットの上位バイトの一時レジスタ(TEMP)を使用して実行されます。この一時レジスタは他の全ての16ビットのレジスタで共有されています。「16ビットのレジスタにアクセスする」(p.109)を参照してください。

カウンター動作中にカウンター(TCNT1)の値を変更すると、TCNT1とOCR1xのレジスタのどれかとの間での比較一致が正しく行われない可能性があります。

TCNT1レジスタへの書き込みを行うと、それに続くタイマー・クロックにおいて、全ての比較ユニットとカウンターの間で比較一致は行われません。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x89) | OCR1A[15:8] | OCR1AH | |||||||

| (0x88) | OCR1A[7:0] | OCR1AL | |||||||

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x8B) | OCR1B[15:8] | OCR1BH | |||||||

| (0x8A) | OCR1B[7:0] | OCR1BL | |||||||

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

比較レジスタは、カウンターの値(TCNT1)と毎回比較される、16ビットの値を保持しています。比較一致によって、比較一致割り込みを発生させたり、OC1x端子に波形出力を発生させることができます。

比較レジスタは16ビット幅のレジスタです。CPUがこれらのレジスタにアクセスする際に、確実に上位バイトと下位バイトが同時に読み書きできるように、このレジスタへのアクセスは8ビットの上位バイトの一時レジスタ(TEMP)を使用して実行されます。この一時レジスタは他の全ての16ビットのレジスタで共有されています。「16ビットのレジスタにアクセスする」(p.109)を参照してください。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x87) | ICR1[15:8] | ICR1H | |||||||

| (0x86) | ICR1[7:0] | ICR1L | |||||||

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

インプット・キャプチャ・レジスタは、ICP1端子(または、タイマー/カウンター1に使用するように設定されたアナログ・コンパレータ出力)に発生するイベントがあるたびに、カウンター(TCNT1)の値と同じ内容に更新されます。インプット・キャプチャ・レジスタはカウンターのTOP値設定としても使用できます。

インプット・キャプチャ・レジスタは16ビット幅のレジスタです。CPUがこれらのレジスタにアクセスする際に、確実に上位バイトと下位バイトが同時に読み書きできるように、このレジスタへのアクセスは8ビットの上位バイトの一時レジスタ(TEMP)を使用して実行されます。この一時レジスタは他の全ての16ビットのレジスタで共有されています。「16ビットのレジスタにアクセスする」(p.109)を参照してください。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x6F) | - | - | ICIE1 | - | - | OCIE1B | OCIE1A | TOIE1 | TIMSK1 |

| Read/Write | R | R | R/W | R | R | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

これらのビットはATmega48/88/168では将来拡張のため予約となっており、リード時は常にゼロになります。

このビットに1が書き込まれていて、ステータス・レジスタのIフラグがセット(グローバル割込みビットが有効に設定)されているとき、タイマー/カウンター1のインプット・キャプチャ割込みが有効になります。対応する割込みベクトル(「割込み」(p.55)を参照)がTIFR1レジスタ中のICF1フラグがセットされた時に実行されます。

これらのビットはATmega48/88/168では将来拡張のため予約となっており、リード時は常にゼロになります。

このビットに1が書き込まれ、ステータスレジスタのIフラグがセット(グローバル割込みビットが有効に設定)されていると、タイマー/カウンター1の比較一致B割り込みが有効になります。対応する割り込みベクトル(55ページの「割込み」を参照)がTIFR1レジスタ中のOCF1Bフラグがセットされた時に実行されます。

このビットに1が書き込まれ、ステータスレジスタのIフラグがセット(グローバル割込みビットが有効に設定)されていると、タイマー/カウンター1の比較一致A割り込みが有効になります。対応する割り込みベクトル(55ページの「割込み」を参照)がTIFR1レジスタ中のOCF1Aフラグがセットされた時に実行されます。

このビットに1が書き込まれ、ステータスレジスタのIフラグがセット(グローバル割込みビットが有効に設定)されていると、タイマー/カウンター1のオーバーフロー割込みが有効になります。対応する割り込みベクトル(55ページの「割込み」を参照)がTIFR1レジスタ中のTOV1フラグがセットされた時に実行されます。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x16 (0x36) | - | - | ICF1 | - | - | OCF1B | OCF1A | TOV1 | TIFR1 |

| Read/Write | R | R | R/W | R | R | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

これらのビットはATmega48/88/168では将来拡張のため予約となっており、リード時は常にゼロになります。

このフラグは、ICP1端子においてキャプチャ・イベントが発生した時にセットされます。WGM13:0ビットにより、インプット・キャプチャ・レジスタ(ICR1)をTOP値として使用するように設定されている場合、カウンターがTOP値に達するとICF1フラグがセットされます。

ICF1フラグは、インプット・キャプチャ割込みベクトルが実行されると自動的にクリアされます。別の方法として、このビット位置に論理値1を書き込むことによりICF1フラグをクリアすることも出来ます。

これらのビットはATmega48/88/168では将来拡張のため予約となっており、リード時は常にゼロになります。

このフラグは、カウンター(TCNT1)と比較レジスタB(OCR1B)の値が一致した時、その次のクロックでセットされます。

比較一致強制ビット(FOC1B)による比較一致では、OCF1Bフラグはセットされないことにご注意ください。

OCF1Bフラグは、比較一致B割込みベクトルが実行されると自動的にクリアされます。別の方法として、このビット位置に論理値1を書き込むことによりOCF1Bフラグをクリアすることも出来ます。

このフラグは、カウンター(TCNT1)と比較レジスタB(OCR1A)の値が一致した時、その次のクロックでセットされます。

比較一致強制ビット(FOC1A)による比較一致では、OCF1Aフラグはセットされないことにご注意ください。

OCF1Aフラグは、比較一致B割込みベクトルが実行されると自動的にクリアされます。別の方法として、このビット位置に論理値1を書き込むことによりOCF1Aフラグをクリアすることも出来ます。

このフラグがセットされるタイミングは、WGM13:0ビットの設定によって決まります。通常モード、CTCモードでは、TOV1フラグはタイマー・オーバーフローの際にセットされます。WGM13:0ビットの他の設定におけるTOV1フラグの動作については、Table 15-4 (p.131)を参照してください。

TOV1フラグは、タイマー/カウンター1オーバーフロー割込みベクトルが実行されると自動的にクリアされます。別の方法として、このビット位置に論理値1を書き込むことによりTOV1フラグをクリアすることも出来ます。