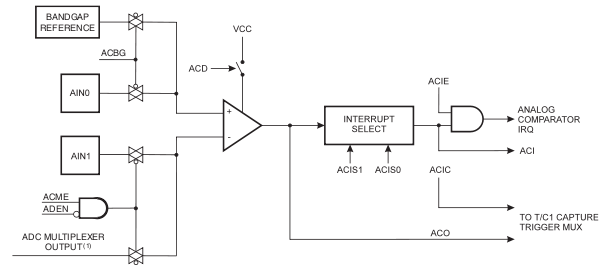

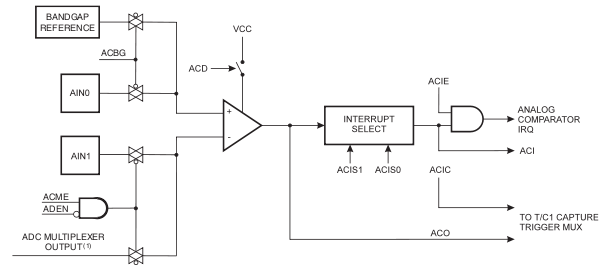

アナログ・コンパレータは非反転入力端子AIN0と、反転入力端子AIN1の入力を比較します。 非反転入力AIN0端子の電圧が反転入力AIN1端子の電圧よりも高いとき、アナログ・コンパレータの出力AC0がセットされます。 コンパレータ出力は、タイマー/カウンター1のインプット・キャプチャ機能のトリガー入力として使用できます。 さらに、コンパレータ専用の独立した割り込みをトリガーすることができます。 ユーザー・プログラムにより、コンパレータ出力の立ち上がりエッジ、立ち下がりエッジ、両方のエッジによる割り込みトリガーを選択可能です。 コンパレータと周辺回路のブロック図をFigure 22-1に示します。

ADCマルチプレクス入力を使用するためには、「消費電力を最小にするために」(p.40)に記載されているADCパワー低減ビット(PRADC)に0を書き込んで無効にしておく必要があります。

注意:

アナログ・コンパレータの反転入力の代わりに、ADC7..0の入力のいずれかを選択して使用することができます。 ADCマルチプレクサを使用して、この入力を選択するため、同期脳を使用する場合はA/Dコンバーターの機能を停止しておく必要があります。 アナログ・コンパレータ・マルチプレクサ有効ビット(ADCSRBレジスタのACMEビット)がセットされていて、A/Dコンバータが機能停止している(ADCSRAレジスタのADENビットが0の状態)場合、Table 22-1にあるように、ADMUXレジスタのMUX2..0ビットにより、アナログ・コンパレータの反転入力の代わりに使用する端子が選択されます。 ACMEビットがクリアされているか、ADENビットがセットされている場合、ANI1端子がアナログ・コンパレータの反転入力に接続されます。

| ACME | ADEN | MUX2..0 | アナログ・コンパレータの反転入力 |

|---|---|---|---|

| 0 | x | xxx | AIN1 |

| 1 | 1 | xxx | AIN1 |

| 1 | 0 | 000 | ADC0 |

| 1 | 0 | 001 | ADC1 |

| 1 | 0 | 010 | ADC2 |

| 1 | 0 | 011 | ADC3 |

| 1 | 0 | 100 | ADC4 |

| 1 | 0 | 101 | ADC5 |

| 1 | 0 | 110 | ADC6 |

| 1 | 0 | 111 | ADC7 |

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x7B) | - | ACME | - | - | - | ADTS2 | ADTS1 | ADTS0 | ADCSRB |

| Read/Write | R | R/W | R | R | R | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

このビットに1が書き込まれていて、A/Dコンバータが停止している(ADCSRAレジスタのADENビットが0)の場合、ADCマルチプレクサにより、アナログ・コンパレータの反転入力が選択されます。 このビットに0が書き込まれている場合、AIN1端子がアナログ・コンパレータの反転入力に接続されます。 このビットの詳しい機能については、「アナログ・コンパレータ・マルチプレクス入力」(p.240)を参照してください。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0x30 (0x50) | ACD | ACBG | ACO | ACI | ACIE | ACIC | ACIS1 | ACIS0 | ACSR |

| Read/Write | R/W | R/W | R | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | N/A | 0 | 0 | 0 | 0 | 0 |

このビットに1が書き込まれている場合、アナログ・コンパレータへの電源供給が停止します。 このビットを使うとアナログ・コンパレータをいつでも停止することができ、アクティブ・モード、アイドル・モードにおける消費電力を低減することができます。 ACDビットを変更するときには、ACSRレジスタのACIEビットをクリアしてアナログ・コンパレータ割り込みを無効にしておく必要があります。 そうしないと、このビットの変更の際に、割り込みが発生する場合があります。

このビットをセットすると、固定値を持つバンドギャップ電圧リファレンスの出力が、アナログ・コンパレータの非反転入力に接続されます。 このビットがクリアされている場合、AIN0端子がアナログ・コンパレータの非反転入力に接続されます。 バンドギャップ電圧リファレンスをアナログ・コンパレータの入力として使用する場合、電圧が安定するまでに一定の時間が必要です。 安定した電圧を使用しないと、最初の変換動作において不正確な値が出力される場合があります。 「内蔵の電圧リファレンス」(p.47)を参照してください。

アナログ・コンパレータの出力は同期回路を通して、AC0ビットに直接接続されています。 同期動作のため、1 - 2クロック・サイクルの遅延が発生します。

ACIS1、ADIS0ビットによって設定されているコンパレータ出力変化による割り込みが発生した場合、このビットがハードウェアによりセットされます。 ACIEビットがセットされていて、SREGのIビットがセットされている場合、アナログ・コンパレータ割り込み処理が実行されます。 対応する割り込みベクトルが実行されると、ACIビットはハードウェアによってクリアされます。 別の方法としては、このフラグに1を書き込むことでクリアすることができます。

ACIEビットに1が書き込まれていて、ステータス・レジスタのIビットがセットされている場合、アナログ・コンパレータ割り込みが有効になります。 0が書き込まれている場合、同割り込みは無効となります。

このビットに1を書き込むと、タイマー/カウンター1のインプット・キャプチャ機能のトリガーをアナログ・コンパレータによって行うことができます。 このとき、コンパレータ出力はインプット・キャプチャ回路の入力部に直接接続され、タイマー/カウンター1のノイズ抑制回路、エッジ選択機能を利用することができます。 0が書き込まれている場合、アナログ・コンパレータとインプット・キャプチャ機能との間に接続関係はありません。 コンパレータによってタイマー/カウンター1のインプット・キャプチャ割り込みを発生させるためには、タイマー割り込みマスク・レジスタ(TIMSK1)のICIE1ビットをセットしておく必要があります。

このビットにより、アナログ・コンパレータ割り込みをいつ発生させるかを決定します。 各設定をTable 22-2に表します。

| ACIS1 | ACIS0 | 割り込みモード |

|---|---|---|

| 0 | 0 | コンパレータの出力が変化したら割り込み発生 |

| 0 | 1 | (予約) |

| 1 | 0 | コンパレータ出力の立ち下がりエッジで割り込み発生 |

| 1 | 1 | コンパレータ出力の立ち上がりエッジで割り込み発生 |

ACIS1/ACIS0ビットを変更する際は、ACSRレジスタのACIEビットをクリアしてアナログ・コンパレータ割り込みを無効にしておく必要があります。 そうしないと、このビットの変更の際に割り込みが発生する場合があります。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| (0x7F) | - | - | - | - | - | - | AIN1D | AIN0D | DIDR |

| Read/Write | R | R | R | R | R | R | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

このビットはATmega48/88/168では未使用で、読み出し時には常に0になります。

このビットに1を書き込むと、AIN1/0端子のデジタル入力バッファが無効になり、それぞれの端子に対応するポートのPINレジスタのビットは常に0になります。 AIN1/0端子にアナログ信号を入力していて、その端子をデジタル入力として使用しない場合は、このビットに1を書き込みデジタル入力バッファでの消費電力が少なくなるようにしてください。