マスター

汎用同期非同期シリアル送受信器(USART)は、マスターSPIの規格にしたがった動作をすることができます。 UMSELn1:0ビットを両方とも1にセットすると、USARTのマスターSPIモード(MSPIM)が有効になります。 この動作モードでは、SPIマスター動作のための制御回路がUSARTのモジュールをコントロールします。 制御対象のモジュールには、送受信のシフト・レジスタとバッファ、そしてボーレート・ジェネレータが含まれます。 パリティ・ジェネレータおよびパリティ・チェッカー、データとクロックのリカバリ回路、そしてRX、TX信号を制御する回路は無効になります。 USARTのRX、TX信号の制御回路は、SPI通信共通の制御回路に置き換わります。 ただし、端子の制御回路と割込み発生回路は、どちらのモードでも同様の動作です。

レジスタのI/Oアドレスは、両モードとも同じです。ただし、MSPIMを使用している場合は制御レジスタの機能が異なる場合があります。

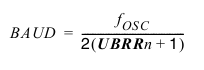

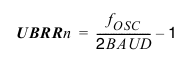

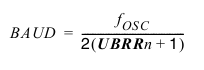

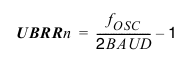

クロック生成回路により、送受信器の基本クロックが作り出されます。USARTのMSPIMモードでは、内部クロック生成(マスター動作)のみサポートされます。 そのため、MSPIMモードでUSARTが正しく動作するためには、XCKn端子の入出力方向レジスタ(DDR_XCKn)は1に(つまり出力に)設定されていなければなりません。 DDR_XCKnの設定は、USARTのMSPIMモードを有効にする(TXENnとRXENnビットに1をセットする)よりも前に行っておいた方が好ましいです。 MSPIMモードで使用されている内部クロック生成する部分については、USARTの同期マスター・モードと同じです。 したがって、ボーレートとUBRRnレジスタの設定は同じ計算式によって算出できます(Table20-1参照)。

Table 20-1. ボーレート・レジスタ設定の計算式

| 動作モード | ボーレートの計算式(1) | UBRRnの値の計算式 |

|---|---|---|

| 同期モード マスター |

|

|

| BAUD | ボーレート(1秒あたりのビット数、bps) |

|---|---|

| fOSC | システム・クロックの周波数 |

| UBRRn | UBRRnH、およびUBRRnLレジスタの内容 (0-4095) |

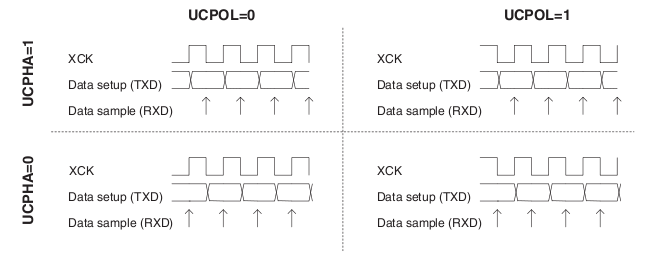

シリアル・データに対する、XCKn(SCK)の位相と極性には全部で4つの組み合わせがあり、これは、UCPHAnビットとUCPOLnビットにより決定されます。 データ転送のタイミング・ダイアグラムをFigure20-1に示します。 データ信号が安定するまでの十分な時間を確保するため、XCKn信号のそれぞれ別々のエッジにおいて、データ・ビットのシフト動作とラッチ動作が行われます。 UCPOLnとUCPHAnの機能をTable20-2にまとめます。 通信実行中に、これらのビットの変更を行うと、送信、受信ともにデータ異常が発生することになりますので、ご注意ください。

Table 20-2. UCPOLn と UCPHAn の機能

| UCPOLn | UCPHAn | SPIモード | 前方エッジ | 後方エッジ |

|---|---|---|---|---|

| 0 | 0 | 0 | ラッチ動作(立ち上がり) | シフト動作(立ち下がり) |

| 0 | 1 | 1 | シフト動作(立ち上がり) | ラッチ動作(立ち下がり) |

| 1 | 0 | 2 | ラッチ動作(立ち下がり) | シフト動作(立ち上がり) |

| 1 | 1 | 3 | シフト動作(立ち下がり) | ラッチ動作(立ち上がり) |

Figure 20-1. UCPHAn、UCPOLnとデータ転送のタイミング・ダイアグラム

MSPIMモードでのシリアル・フレームは、1キャラクタあたり8ビットに設定されています。 MSPIMモードのUSARTでは、二種類のフォーマットを使用できます。

各フレームは、データのLSBまたはMSBから始まります。 それにつづいて、全部で8つのデータ・ビットがつづき、MSBまたはLSBで終了します。 1フレームの送信が完了すると、新しいフレームが直後に続くか、あるいは、通信ラインが待機状態(High)にセットされます。

UCSRnCレジスタのUDORDnビットにより、MSPIMモードのUSARTで使用するフレームのフォーマットを設定します。 送受信ともに同じ設定を使用します。 通信実行中に、これらのビットの変更を行うと、送信、受信ともにデータ異常が発生することになりますので、ご注意ください。 16ビットのデータ通信は、UDRnレジスタに二つのデータバイトを書き込むことにより実現できます。 16ビットの値がシフトされ送信完了すると、UART送信完了割込みが発生します。

USARTのMSPIモードの初期化は、通信を行う前に設定しておかなければなりません。 初期化の手順で通常、ボーレートの設定、マスター動作モード(DDR_XCKnを1にセット)の設定、フレーム・フォーマットの設定、そして送信器と受信器の有効化を行います。 送信器については、単独で動作させることできます。 割込みによるUSART動作の制御を行うためには、グローバル割込みフラグをクリア(つまり、全割込みを禁止)して初期設定を行う必要があります。

注意: XCKn出力端子の初期化を確実に行うため、送信器を有効に設定する際に、ボーレート・レジスタ(UBRRn)はゼロに設定してください。 通常のUSARTの動作モードとは異なり、送信器が有効になった後、最初の送信を開始する前に、UBRRnレジスタを希望の値に設定しなければなりません。 リセット直後のUSART初期化においては、UBRRnレジスタはゼロになっているため、送信器を有効にする前にUBRRnをゼロに設定する必要はありません。

ボーレート、データ・モード、あるいはフレーム・フォーマットを変更して初期化を再度行う前には、レジスタ変更中に通信が行われることのないようにしてください。 TXCnフラグにより、送信が全て完了したことを確認でき、また、RXCnフラグにより受信バッファ内に読み出されていないデータがないことを確認できます。 この用途にTXCnフラグを使用するため、TXCnフラグは各送信の前に(UDRnに書き込みを行う前に)クリアされていなければなりません。

下記に、簡略化したUSART初期化のサンプルコードを、同等の機能を、アセンブリ言語とC言語の関数で示します。 この例ではポーリング処理を行う(割込みを使用しない)ものとしています。ボーレートは、関数の引数パラメータとして与えられています。 アセンブリ言語では、ボーレートのパラメータはr17:r16レジスタに格納されているものとします。

| アセンブリ言語での例(1) |

USART_Init: clr r18 out UBRRnH,r18 out UBRRnL,r18 ; XCKn端子を出力に設定し、マスター・モードを有効にする sbi XCKn_DDR, XCKn ; MSPIモード、およびSPIデータモード0を設定 ldi r18, (1<<UMSELn1)|(1<<UMSELn0)|(0<<UCPHAn)|(0<<UCPOLn) out UCSRnC,r18 ; 送信器、受信機を有効にする ldi r18, (1<<RXENn)|(1<<TXENn) out UCSRnB,r18 ; ボーレートを設定 ; 重要: ボーレート設定は送信器が有効になった後で行うこと! out UBRRnH, r17 out UBRRnL, r18 ret |

| C言語での例(1) |

void USART_Init( unsigned int baud )

{

UBRRn = 0;

/* XCKn端子を出力に設定し、マスター・モードを有効にする */

XCKn_DDR |= (1<<XCKn);

/* MSPIモード、およびSPIデータモード0を設定 */

UCSRnC = (1<<UMSELn1)|(1<<UMSELn0)|(0<<UCPHAn)|(0<<UCPOLn);

/* 送信器、受信機を有効にする */

UCSRnB = (1<<RXENn)|(1<<TXENn);

/* ボーレートを設定 */

/* 重要: ボーレート設定は送信器が有効になった後で行うこと! */

UBRRn = baud;

}

|

注: 1. 「サンプル・コードについて」(p.7)を参照

USARTをMSPIモードで使用するには、送信器を必ず有効に、つまり、UCSRnBレジスタのTXENnビットを1に設定しなければなりません。 送信器が有効になると、TxDn端子では通常のポートよりも送信器のシリアル出力機能が優先されます。 受信器の有効/無効は選択可能であり、UCSRnBレジスタのRXENnビットを1にすると有効になります。

受信器が有効になると、RxDn端子の通常のポートとしての動作よりも、受信器のシリアル入力機能が優先されます。 XCKn端子はどちらの場合においても、転送クロックとして使用されます。

初期化が完了した時点で、USARTはデータの転送準備ができています。 データ転送は、UDRnレジスタのI/Oアドレスに書き込みを行うことにより開始されます。 これは、送信器側が転送クロックを制御するため、送信、受信両方について同様のことがあてはまります。 UDRnレジスタに書き込まれたデータは、新しい通信フレームを送信する準備ができたとき、送信バッファからシフト・レジスタへと転送されます。

注意: 入力バッファと送信データのバイト数を同期させるため、UDRnレジスタを各バイトの送信のたびに一回ずつ読み出しする必要があります。 入力バッファの動作は通常のUSARTモードと同一であり、オーバーフローが発生すると、バッファにある最初のデータではなく、最後に受信されたキャラクタが失われます。 別の表現をすると、4バイトが、バイト1、バイト2、バイト3、バイト4と転送され、UDRnが全ての転送が完了するまで読み出しされない場合、バイト1ではなく、受信されるはずであったバイト3が失われます。

下記のコーディング例では、簡略化したUSARTのMSPIMモードでの転送機能を、データ・レジスタ・エンプティ(UDREn)フラグと受信完了(RXCn)フラグによるポーリング処理に基づいて実行する関数を示します。 USARTはこの関数の実行前に初期化されている必要があります。 アセンブリ言語での例では、送信されるデータはR16レジスタに格納されており、受信されるデータは関数の復帰時には、同じR16レジスタに格納されます。

この関数は単純に、送信バッファが空になるのをUREnフラグをチェックしながら待機してから、新しい送信データをバッファにロードします。 関数はその後、RXCnフラグを監視して受信バッファにデータが現れるのを待ち、バッファを読み出して値を返します。

| アセンブリ言語での例(1) |

USART_MSPIM_Transfer: ; 送信バッファが空くのを待つ sbis UCSRnA, UDREn rjmp USART_MSPIM_Transfer ; データ (r16) をバッファに転送し、データを送信する out UDRn,r16 ; データの受信を待つ USART_MSPIM_Wait_RXCn: sbis UCSRnA, RXCn rjmp USART_MSPIM_Wait_RXCn ; バッファから受信データを得て、値を返す in r16, UDRn ret |

| C言語での例(1) |

unsigned char USART_Receive( void )

{

/* 送信バッファが空くのを待つ */

while ( !( UCSRnA & (1<<UDREn)) );

/* データをバッファに転送し、データを送信する */

UDRn = data;

/* データの受信を待つ */

while ( !(UCSRnA & (1<<RXCn)) );

/* バッファから受信データを得て、値を返す */

return UDRn;

}

|

注: 1. 「サンプル・コードについて」(p.7)を参照

RXCn、TXCn、UDREnの各フラグと、それぞれに対応する割込みは、MSPIMモードにおいても通常のUSART動作モードと同じです。ただし、受信器のエラー・ステータス・フラグ(FE、DOR、PE)が使用されることはなく、読み出し時には常にゼロとなります。

USARTのMSPIMモードでの送受信器の無効化については、通常のUSART動作モードと同じです。

MSPIMモードのUSARTは、AVR SPIインターフェースと以下の点において完全な互換性があります。

ただし、USARTのMSPIMモードはUSARTモジュールの回路を再利用しているため、その使用にあたっては、SPIインターフェースとは若干異なる点があります。 レジスターのビット操作のちがいに加えて、USARTのMSPIMモードではマスター動作のみがサポートされており、下記の機能は両モジュール間では異なっています。

USARTのMSPIMモードとSPIインターフェースの端子を比較したものをTable20-3(p.204)に示します。

Table 20-3. USARTのMSPIMモードとSPIの端子の比較

| USART_MSPIM | SPI | 注釈 |

|---|---|---|

| TxDn | MOSI | マスター・アウトのみ |

| RxDn | MISO | マスター・インのみ |

| XCKn | SCK | (同じ機能) |

| (N/A) | /SS | USARTのMSPIMモードには無い |

ここでは、USARTモジュールのSPI動作に用いられるレジスタについて解説します。

MSPIモードのUSARTデータ・レジスタ(UDRn)の機能とビットの説明は、通常のUSART動作と同じです。 「UDRn – USART I/Oデータ・レジスタn」(p.189)を参照してください。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| RXCn | TXCn | UDREn | - | - | - | - | - | UCSRnA | |

| Read/Write | R | R/W | R | R | R | R | R | R | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

このフラグ・ビットは、受信バッファに読み出されていないデータが存在する場合にセットされ、受信バッファが空になったとき(未読のデータがない)クリアされます。 受信器を無効にすると、受信バッファの内容は破棄され、したがってRXCnビットはゼロになります。RXCnフラグを用いて、受信完了割込みを発生させることができます(RXCIEnビットの説明を参照)。

このフラグ・ビットは、送信器内のフレームが完全に送出され、送信バッファ(UDRn)に新しいデータが無い場合にセットされます。TXCnフラグは送信完了割込みが実行されると自動的にクリアされます。また、このビットに1を書き込むことによってもクリアできます。 TXCnフラグを用いて、送信完了割込みを発生させることができます(TXCIEnビットの説明を参照)。

UDREnフラグは、送信バッファ(UDRn)が新しいデータを受け取る準備ができているかどうかを表しています。UDREビットが1の場合、バッファは空になっており、したがって書き込みが可能です。UDREnフラグを用いて、データ・レジスタ・エンプティ割込みを発生させることができます(UDRIEビットの説明を参照)。 UDREnはリセット後、送信器の準備ができていることを表すためセットされています。

MSPIモードでは、これらのビットは将来拡張のため予約となっています。将来のデバイスとの互換性を確保するために、UCSRnAレジスタに書き込みを行う場合は、これらのビットをゼロにしておかなければなりません。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| RXCIEn | TXCIEn | UDRIE | RXENn | TXENn | - | - | - | UCSRnB | |

| Read/Write | R/W | R/W | R/W | R/W | R/W | R | R | R | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

このビットに1を書き込むとRXCnフラグによる割込みが有効になります。 RXCIEnビットに1がセットされ、SREGのグローバル割込みフラグに1がセットされ、UCSRnAレジスタのRXCnビットがセットされた場合にのみ、USART受信完了割込みが発生します。

このビットに1を書き込むとTXCnフラグによる割込みが有効になります。 TXCIEnビットに1がセットされ、SREGのグローバル割込みフラグに1がセットされ、UCSRnAレジスタのTXCnビットがセットされた場合にのみ、USART送信完了割込みが発生します。

このビットに1を書き込むとUDREnフラグによる割込みが有効になります。 UDRIEビットに1がセットされ、SREGのグローバル割込みフラグに1がセットされ、UCSRnAレジスタのUDREnビットがセットされた場合にのみ、USARTデータ・レジスタ・エンプティ割込みが発生します。

このビットに1を書き込むと、MSPIMモードのUSART受信器が有効になります。 受信器が有効になると、RxDn端子としての機能が通常のポートの動作よりも優先されます。MSPIモードにおいては、送信器が通信クロックを制御し、マスター動作のみがサポートされているため、受信器のみを有効にすること(RXENn=1、TXENn=0に設定)には意味がありません。

このビットに1を書き込むと、USARTの送信器が有効になります。 送信器が有効になると、TxDn端子としての機能が通常のポートの動作よりも優先されます。 送信器を無効にする(TXENnにゼロを書き込む)場合、処理中および待機中の通信が完了するまで、つまり、送信シフト・レジスタと送信バッファ・レジスタに送信データが残っていない状態になるまで、送信器は無効になりません。 送信器が無効になると、TxDn端子の機能優先は解除されます。

MSPIモードでは、これらのビットは将来拡張のため予約となっています。将来のデバイスとの互換性を確保するために、UCSRnBレジスタに書き込みを行う場合は、これらのビットをゼロにしておかなければなりません。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| UMSELn1 | UMSELn0 | - | - | - | UDORDn | UCPHAn | UCPOLn | UCSRnC | |

| Read/Write | R/W | R/W | R | R | R | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

これらのビットにより、USARTの動作モードをTable20-4にあるとおりに選択します。 「UCSRnC – USARTコントロール/ステータス・レジスタnC」(p.191)にある、通常のUSART動作での説明をを参照してください。 MSPIMモードは、UMSELnビットを両方とも1にセットすると有効になります。 MSPIMモードを有効にする書き込みの際に、UDORDn、UCPHAn、UCPOLnビットを同時に設定することができます。

Table 20-4. UMSELnビットの設定

| UMSELn1 | UMSELn0 | モード |

|---|---|---|

| 0 | 0 | 非同期USART |

| 0 | 1 | 同期USART |

| 1 | 0 | (予約) |

| 1 | 1 | マスターSPI(MSPIM) |

MSPIモードでは、これらのビットは将来拡張のため予約となっています。将来のデバイスとの互換性を確保するために、UCSRnCレジスタに書き込みを行う場合は、これらのビットをゼロにしておかなければなりません。

このビットを1にセットすると、データ・ワードのLSBが先に送出されます。ゼロにセットすると、データ・ワードのMSBが先に送出されます。 詳細は、20.4 SPIデータ・フォーマットのフレーム・フォーマットを参照してください。

UCPHAnビットの設定により、データのサンプリング動作をXCKnクロックの前方エッジと後方エッジのどちらで行うかを決定します。 詳細は、20.4 SPIデータ・フォーマットのフレーム・フォーマットを参照してください。

UCPOLnビットの設定により、XCKnクロックの極性を設定します。UCPOLnビットとUCPHAnビットの組み合わせによりデータ転送のタイミングが決定されます。 詳細は、20.4 SPIデータ・フォーマットのフレーム・フォーマットを参照してください。

MSPIモードにおけるボーレート・レジスタの説明は通常のUSART動作と同じです。「UBRRnL、UBRRnH – USARTボーレート・レジスタ」(p.193)を参照してください。