USARTは、マスターSPIモードで使用することもできます。「USARTのSPIモード」 (p.198)を参照してください。「消費電力を最小にするために」 (p.40)に記載されている、USART電力低減モード・ビット(PRUSART0)にゼロを書き込んで電力低減を無効にしておく必要があります。

汎用同期非同期シリアル送受信器(USART)は、様々な設定に対応できるシリアル通信デバイスです。

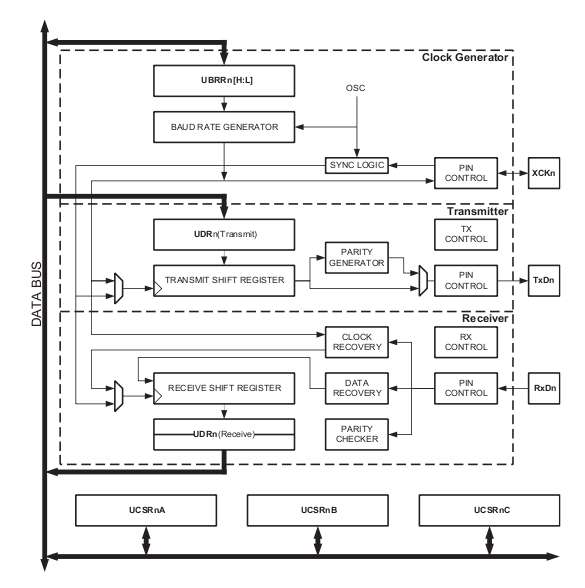

USARTの簡略ブロック図をFigure19-1に示します。 CPUからアクセス可能なI/Oレジスタ、および入出力端子は太字で記されています。

ブロック図の点線で囲まれた部分はUSARTの三つの主要部です。(上から)クロック生成器、送信器、受信器です。 コントロール・レジスタは全てのユニットで共有されています。

クロック生成器には、同期スレーブ動作で用いられる外部クロックの同期回路と、ボーレート・ジェネレータがあります。 XCKn(転送クロック)端子は同期通信モードでのみ使用します。

送信器には、単一の書き込みバッファ、シリアル・シフト・レジスタ、パリティ生成回路、そして様々な通信フレームを処理するための制御回路があります。 書き込みバッファの存在により、通信フレーム間で遅延を発生させることなく、連続してデータを転送することが可能です。

受信器には、クロック/データのリカバリ・ユニットがあり、USARTモジュールの中で最も複雑な部分です。 リカバリ・ユニットは非同期通信で用いられます。 リカバリ・ユニットに加えて、受信器にはパリティ・チェッカー、制御回路、シフト・レジスタ、および2レベルの受信バッファ(UDRn)があります。 受信器では、送信器と同じ通信フレーム・フォーマットに対応し、フレーム・エラー、データ・オーバーラン、パリティ・エラーを検出できます。

注意: 1. USART0の端子の配置については、Figure 1-1(p.2)、およびTable 13-9(p.83)を参照

クロック生成回路では、送信器と受信器で使用する基本クロックが生成されます。 USARTには、4つのクロック動作モードがあります。 「非同期通常モード」、「非同期倍速モード」、「同期マスター・モード」、「同期スレーブ・モード」です。 USARTコントロール/ステータス・レジスタC(UCSRnC)のUMSELnビットにより、非同期動作と同期動作を選択します。 倍速動作(非同期モードのみ)はUCSRnAレジスタのU2Xnビットにより設定します。 同期モードを使用している(UMSELn = 1)場合、XCKn端子の入出力方向レジスタ(DDR_XCKn)により、クロック源を内部にするか(マスター・モード)、外部にするか(スレーブ・モード)を設定します。 XCKn端子は同期モードを使用する場合のみ、有効になります。

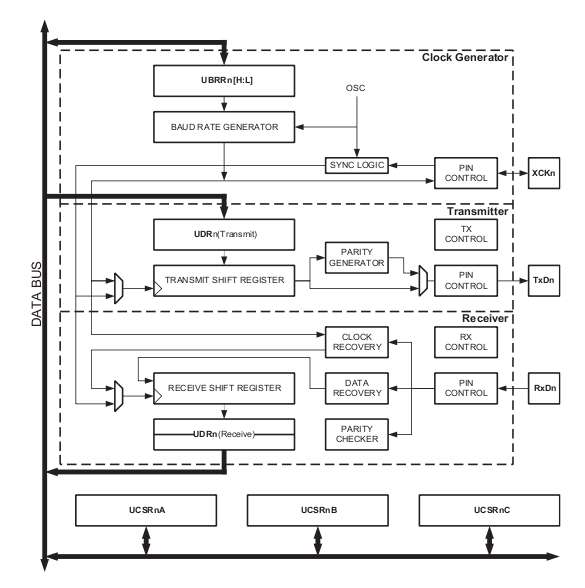

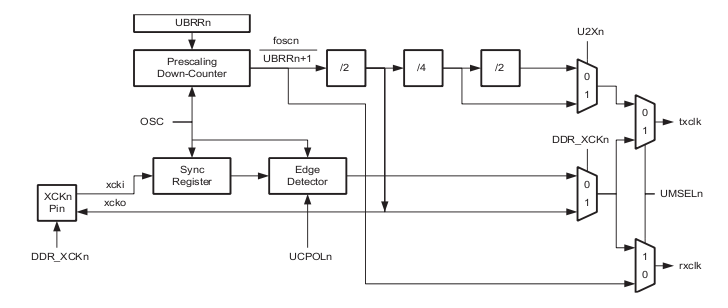

Figure 19-2に、クロック生成回路のブロック図を示します。

| 各信号の内容 | |

| txclk | 送信クロック(内部信号) |

|---|---|

| rxclk | 受信クロック(内部信号) |

| xcki | XCK端子からの入力(内部信号)。同期スレーブ動作で使用 |

| xcko | XCK端子への出力(内部信号)。同期マスター動作で使用 |

| f_osc | XTAL端子の周波数(システム・クロック) |

内蔵のクロック生成機能は非同期モード、および同期マスター・モードで使用されます。 この節の各用語の意味については、Figure19-2を参照してください。

USARTのボーレート・レジスタ(UBRRn)と、それに接続されているダウン・カウンタは、プログラム可能な分周器、つまりボーレート・ジェネレータとして機能します。 ダウン・カウンタはシステム・クロックによりカウント動作を行い、値がゼロになるか、UBRRnレジスタに書き込みがあった際に、UBRRnレジスタの値がロードされます。 クロックは、カウンタがゼロになるごとに発生します。 このクロックはボーレート・ジェネレータのクロック出力(= fosc/(UBRRn+1))となります。 送信器では、モードに応じて、このボーレート・ジェネレータのクロック出力を、2, 8, 16のいずれかで分周します。 受信器のクロック/データ・リカバリ・ユニットでは、ボーレート・ジェネレータの分周されていない出力が使用されます。 ただし、リカバリ・ユニットでは、UMSELn、U2Xn、DDR_XCKnビットにより決まる状態に応じて、2, 8, 16のいずれかのステート数を持つステート・マシンを使用します。

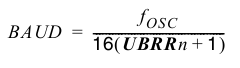

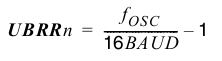

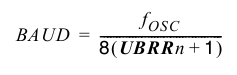

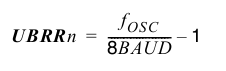

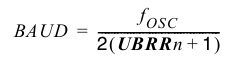

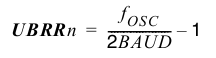

Table 19-1に、内蔵のクロック生成機能を用いる各モードでの、ボーレート(1秒あたりのビット数)とUBRRnレジスタの値の計算式を示します。

| 動作モード | ボーレート計算式(1) | UBRRnの値の計算式 |

|---|---|---|

| 非同期通常モード(U2Xn = 0) |

|

|

| 非同期倍速モード(U2Xn = 1) |

|

|

| 同期マスター・モード |

|

|

注意: 1.ボーレートは1秒あたりの転送レート(bps)として定義

| BAUD | ボーレート(1秒あたりのビット数、bps) |

|---|---|

| f_OSC | システム・クロックの周波数 |

| UBRRn | UBRRnH、UBRRnLレジスタの内容(0-4095) |

Table19-9(p.194)に、システム・クロック周波数に対応するUBRRnの値の例がいくつか示されています。

UCSRnAレジスタのU2Xnビットをセットすることによって、転送速度を二倍にすることができます。 このビットは非同期動作モードでのみ有効です。 同期動作モードでは、このビットをゼロにしてください。

このビットをセットすると、通常16に設定されているボーレート分周カウンタの分周比を8に設定することにより、非同期通信での転送速度を二倍にします。ただし、この設定において受信器は、クロック/データ・リカバリで半分の数のサンプリング(16→8に減少)しか利用できないため、倍速動作を使用する場合、ボーレート設定とシステム・クロックには、より高い精度が要求されます。 送信器についての機能低下はありません。

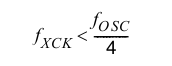

外部クロックは、同期スレーブ動作モードで使用します。 この節の各用語の意味については、Figure19-2を参照してください。

XCKn端子からの外部クロック入力は、同期レジスタ回路によりサンプリングされ、回路全体が不安定な状態に陥る可能性をできるだけ少なくします。 同期レジスタ回路の出力はエッジ検出回路へと伝達されてから、送受信器により使用されます。 このしくみにより、2CPUクロック・サイクルの遅延が発生し、XCKn外部クロックの最大周波数には下記の式による制限があります。

f_oscの値はシステム・クロック源の安定度によっては変動することに注意してください。 したがって、周波数の変動によってデータを消失する可能性をなくすため、いくらかの余裕をもたせておくことが推奨されます。

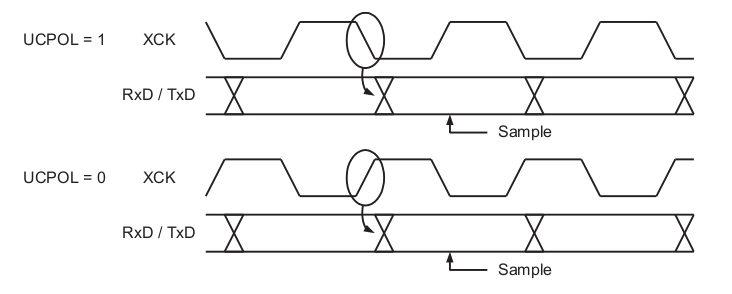

同期モードを使用している(UMSELn = 1)場合、XCKn端子はクロック入力(スレーブ・モード)、またはクロック出力(マスター・モード)として使用します。 クロックのエッジに対する、データのサンプリングや変更タイミングの関係は、どちらのモードでも同じです。 動作の基本原則として、データ入力(RxDn)のサンプリングが行われるXCKnのクロック・エッジと、データ出力(TxDn)が行われるエッジとは、逆のエッジになっています。

UCRSCレジスタのUCPOLnビットにより、XCKnクロック・エッジのうち、データ・サンプリングに用いるエッジとデータの変更に用いるエッジを選択します。 Figure19-3に示すとおり、UCPOLnビットがゼロの場合、データはXCKnの立ち上がりエッジにおいて変化し、立ち下がりエッジにおいてサンプリングされます。 UCPOLnビットがセットされている場合、データはXCKnの立ち下がりエッジにおいて変化し、立ち上がりエッジにおいてサンプリングされます。

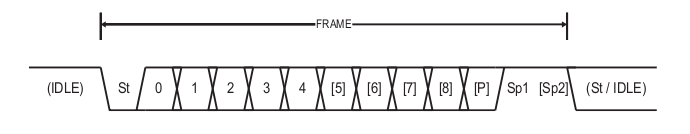

一個のシリアル通信フレームは、データビットからなるキャラクタ1個と、同期用のビット(スタート、およびストップ・ビット)により定義され、エラーチェックのためのパリティ・ビットが追加される場合があります。USARTでは、下記の組み合わせ30種類のフレームを有効なフォーマットとして扱います。

1つのフレームはスタート・ビットにより始まり、その後データの最下位ビット(LSB)がつづきます。そして、最大9ビットまで次のビットがつづき、最上位ビット(MSB)で終了します。 パリティが有効に設定されている場合は、パリティ・ビットがデータ・ビット列の直後に挿入され、ストップ・ビットがその後につづきます。 1フレームの送信が完了すると、即座に次のフレームをつづけて送信するか、まはた通信ラインを待機状態(High)にセットすることができます。

Figure 19-4には、フレーム・フォーマットの可能な組み合わせについて図示したものです。角カッコで囲まれたビットはオプション選択可能なものです。

| St | スタート・ビット、常にLow |

|---|---|

| (n) | データ・ビット (0 から 8) |

| P | パリティ・ビット、奇数または偶数 |

| Sp | ストップ・ビット、常にHigh |

| IDLE |

待機状態。通信ライン(TxD、RxD)では転送が行われていない状態。

待機状態の通信ラインは必ずHighになっていなければなりません。 |

USARTで使用する通信フレーム・フォーマットは、UCSRnBレジスタ、UCSRnCレジスタにあるUCSZn2:0ビット、UPMn1:0ビット、USBSnビットにより、設定します。 送信器と受信器では同じ設定を使用します。 これらのビットのいずれかを通信中に変更すると、処理中の通信データは送受信器ともに異常なデータ値となってしまうことに注意してください。

USARTのキャラクタ・サイズ(UCSZn2:0)ビットにより通信フレーム中ののデータ・ビットの数を選択します。 USARTパリティ・モード(UPMn1:0)ビットにより、パリティ・ビットの有無と種類を設定します。 USARTストップ・ビット選択(USBSn)ビットによって、1、または2のストップ・ビットを選択します。 したがって、FE(フレーム・エラー)の検出は、最初のストップ・ビットがゼロになる時点でのみ行われます。

パリティ・ビットの算出は、全てのデータ・ビットの排他的論理和をとることで行われます。 奇数パリティが使用されている場合、排他的論理和の結果を反転します。 パリティ・ビットとデータ・ビットの関係は下記のようになります。

| P_even | 偶数パリティを使用する場合のパリティ・ビット |

|---|---|

| P_odd | 奇数パリティを使用する場合のパリティ・ビット |

| d_n | キャラクタ中の第nビット |

パリティ・ビットを使用する場合、通信フレーム中の最後のデータ・ビットと最初のストップ・ビットの間にパリティ・ビットが配置されます。

USARTは通信を行う前に初期化する必要があります。 初期化の手順は通常、ボーレート、フレーム・フォーマットを設定し、使用法に応じて送信器や受信器を有効にします。 割込みを利用してUSARTを動作させる場合は、初期化の実行中はグローバル割込みフラグをクリア(全割込みを無効)にしておく必要があります。

ボーレート、あるいはフレーム・フォーマットの変更をともなう再初期化を行う前には、レジスタを変更している間に通信処理が行われないようにしておく必要があります。 TXCnフラグを利用して送信器が全ての送信を完了したことをチェックでき、RXCフラグにより受信器のバッファに読み出しされていないデータが残っていないことを確認できます。 この用途にTXCnフラグを使用する場合、TXCnフラグは送信の度に(UDRnレジスタに書き込みが行われる前に)クリアしておく必要があります。

下記に、簡単なUSART初期化のコーディング例を、アセンブリ言語とC言語で同一の機能を書いたものを示します。 サンプル・コードではポーリング(割込みを使用しない)処理と固定のフレーム・フォーマットによる非同期動作を前提としています。 ボーレート値は関数の引数パラメータとして与えられます。

アセンブリ言語の例では、ボーレート値はr17:r16レジスタに格納されているという前提です。

| アセンブリ言語での例(1) |

USART_Init: ; ボーレートの設定 out UBRRnH, r17 out UBRRnL, r16 ; 受信器、送信器を有効にする ldi r16, (1<<RXENn)|(1<<TXENn) out UCSRnB,r16 ; フレーム・フォーマットの設定:8データビット、2ストップ・ビット ldi r16, (1<<USBSn)|(3<<UCSZn0) out UCSRnC,r16 ret |

| C言語での例(1) |

#define FOSC 1843200 // クロック周波数

#define BAUD 9600

#define MYUBRR FOSC/16/BAUD-1

void main( void )

{

...

USART_Init(MYUBRR)

...

}

void USART_Init( unsigned int ubrr)

{

/* ボーレートの設定 */

UBRR0H = (unsigned char)(ubrr>>8);

UBRR0L = (unsigned char)ubrr;

/* 受信器、送信器を有効にする */

UCSR0B = (1<<RXEN0)|(1<<TXEN0);

/* フレーム・フォーマットの設定:8データビット、2ストップ・ビット */

UCSR0C = (1<<USBS0)|(3<<UCSZ00);

}

|

注: 1. 「サンプル・コードについて」(p.7)を参照

フレーム・フォーマットをパラメータとし、割込みを禁止するなど、より高機能な初期化ルーチンを作成することもできます。 しかし、多くのアプリケーション例ではボーレートや制御レジスタの設定値は固定のものを使用するので、初期化コードは直接メインルーチン内に置くか、他のI/Oモジュールの初期化コードに含めてしまうことができます。

USART送信器は、UCSRnBレジスタの送信器有効(TXEN)ビットをセットすることにより有効になります。 送信器が有効になっている場合、TxDn端子の通常のポートとしての機能よりもUSART機能が優先され、送信器のシリアル出力として機能します。 ボーレート、動作モード、フレーム・フォーマットは、送信を開始する前に設定しておかなければなりません。 同期モードを使用する場合は、XCKn端子のクロックが転送クロックとして使用されます。

データの送信は、送信バッファに送信データを転送することにより開始されます。 CPUからUDRnレジスタのI/Oアドレスに書き込みを行うことで、送信バッファに値を転送することができます。 送信バッファ内に取り込まれたデータは新しいフレームを送信する準備が出来次第、シフト・レジスタへと転送されます。 待機状態(処理中の転送データがない状態)、あるいは、直前のフレームの転送での最後のストップ・ビットの直後に、でシフト・レジスタに新しい値が書き込まれます。 シフト・レジスタに新しいデータが転送されると、動作モードに応じて、ボーレート・レジスタとU2Xnビットによる設定、あるいはXCKnクロックによって決まる転送速度で、一つ分の通信フレームの転送が行われます。

下記のコーディング例は、データ・レジスタ・エンプティ(UDREn)フラグを用いたポーリング処理によるUSART送信の関数を示しています。 8ビット未満のデータ・ビットのフレームを使用する場合、UDRnレジスタに書き込む際の未使用の上位ビットは無視されます。 この関数を使用する前に、USARTを初期化しておく必要があります。 アセンブリ言語の例では、送信データはR16レジスタに格納されているものと仮定します。

| アセンブリ言語の例(1) |

USART_Transmit: ; 送信バッファが空になるのを待つ sbis UCSRnA,UDREn rjmp USART_Transmit ; データ(r16)をバッファに書き込み、データを送信 out UDRn,r16 ret |

| C言語の例(1) |

void USART_Transmit( unsigned char data )

{

/* 送信バッファが空になるのを待つ */

while ( !( UCSRnA & (1<<UDREn)) )

;

/* データ(r16)をバッファに書き込み、データを送信 */

UDRn = data;

}

|

注: 1. 「サンプル・コードについて」(p.7)を参照

この関数は単純に、UDREnフラグをチェックすることで送信バッファが空になるのを待ち、その後新しい送信データをロードします。 データ・レジスタ・エンプティ割込みを利用する場合は、割込み処理ルーチンによってデータをバッファに書き込みます。

9ビット長のキャラクタを使用する(UCSZn = 7)場合、9番目のビットをUCSRnBレジスタのTXB8ビットに書き込んだ後、キャラクタの低位8ビットをUDRnレジスタに書き込んでください。 下記のコーディング例は、9ビット長のキャラクタを扱う送信関数を示しています。 アセンブリ言語の例では、送信データはR17:R16に格納されているものと仮定します。

| アセンブリ言語の例(1)(2) |

USART_Transmit: ; 送信バッファが空になるのを待つ sbis UCSRnA,UDREn rjmp USART_Transmit ; r17にある第9ビットをTXB8に書き込む cbi UCSRnB,TXB8 sbrc r17,0 sbi UCSRnB,TXB8 ; データの低位ビット(r16)をバッファに書き込み、データを送信 out UDRn,r16 ret |

| C言語の例(1)(2) |

void USART_Transmit( unsigned int data )

{

/* 送信バッファが空になるのを待つ */

while ( !( UCSRnA & (1<<UDREn))) )

;

/* 第9ビットをTXB8に書き込む */

UCSRnB & ~(1<<TXB8);

if ( data & 0x0100 )

UCSRnB |= (1<<TXB8);

/* データの低位ビット(r16)をバッファに書き込み、データを送信 */

UDRn = data;

}

|

注意: 1. この送信関数は汎用的なものとして書かれています。 UCSRnBレジスタの他のビット内容に変更がない場合、さらに最適化することが可能です。 例えば、初期化が完了した後では、UCSRnBレジスタのうちTXB8ビットのみが使用されます。

注: 1. 「サンプル・コードについて」(p.7)を参照

マルチ・プロセッサ通信モードや他のプロトコルでの処理、たとえば同期処理などに、第9ビットをアドレス・フレームとして使用することができます。

USART送信器には状態を表す、USARTデータ・レジスタ・エンプティ(UDREn)と送信完了(TXCn)の2つのステータス・フラグがあります。 どちらのフラグも割込みの発生に使用することができます。

データ・レジスタ・エンプティ(UDREn)フラグは、送信バッファが新しいデータを受け入れる準備ができているかどうかを表しています。 このビットは送信バッファが空のときにセットされ、送信するデータがシフト・レジスタに未転送の状態で送信バッファに残っている場合にクリアされます。 将来のデバイスとの互換性のため、UCSRnAレジスタに書き込みを行うときには、必ずこのビットにゼロを書き込んでください。

UCSRnBレジスタのデータ・レジスタ・エンプティ割込み有効(UDRIEn)ビットに1を書き込むと、UDREnフラグがセットされている間(グローバル割込みフラグが有効になっている場合)USARTデータ・レジスタ・エンプティ割込みが実行されます。 UDRnレジスタに書き込みを行うと、UDREnフラグはクリアされます。 割込みを利用したデータ送信を行う場合、データ・レジスタ・エンプティ割込みルーチン内でUDRnレジスタに新しいデータを書き込んでUDREnフラグをクリアするか、データ・レジスタ・エンプティ割込みを無効にしなければなりません。 でなければ、割込み処理が終了すると同時に、新しい割込みが発生することになります。

送信完了(TXCn)フラグは、送信シフト・レジスタ内の1フレームが完全に送出され、送信バッファに新しいデータが存在しない場合に、1にセットされます。

TXCnフラグは送信完了割込みが実行されると自動的にクリアされます。I/Oアドレス上の同ビットに1を書き込むことによってもクリアすることができます。 TXCnフラグは、送信完了と同時に送信側を受信モードにして、通信バスを明け渡さなければならないような(たとえば、RS-485仕様などの)半二重通信インターフェースでよく使用されます。

UCSRnBレジスタの送信完了割込み有効(TXCIEn)ビットがセットされている場合、TXCnフラグがセットされると(グローバル割込みフラグが有効になっている場合)USART送信完了割込みが実行されます。 送信完了割込みを使用する場合は、割込み処理ルーチンでTXCnフラグをクリアする必要はなく、割込み処理実行により自動的にクリアされます。

パリティ・ジェネレータはシリアル通信フレームのデータに対するパリティ・ビットを算出します。 パリティ・ビットが有効(UPMn1 = 1)が有効になっている場合、送信器の制御回路により、送信フレームの最後のデータ・ビットと最初のスタート・ビットの間にパリティ・ビットが挿入されます。

送信器を無効に設定(TXENにゼロを書き込む)しても、現在通信中で未完了の送信が完了するまで、つまり、送信シフト・レジスタと送信バッファ・レジスタに送信データが無い状態になるまで、送信器は無効になりません。 無効になっている状態では、送信器によるTxDn端子の機能優先も無効になります。

UCSRnBレジスタの受信器有効(RXENn)ビットに1を書き込むと、USART受信器が有効になります。 受信器を有効にすると、RxDn端子の通常の動作よりもUSARTが優先となり受信器のシリアル入力端子として機能するようになります。 ボーレート、動作モード、フレーム・フォーマットの設定は、シリアル受信を行うよりも前に完了しておく必要があります。 同期通信モードを使用する場合、XCKn端子のクロック信号が転送クロックとして使用されます。

受信器は有効なスタート・ビットを検出したときにデータ受信を開始します。 スタート・ビットにつづく各ビットはボーレート設定、あるいはXCKn端子のクロックによりサンプリングされ、そのフレームの最初のストップ・ビットが受信されるまで、受信器シフト・レジスタにシフト入力されます。 二番目のストップ・ビットは受信器では無視されます。

最初のストップ・ビットが受信されたとき、つまり、完全に一つのシリアル通信フレームが受信器シフト・レジスタ内に完成したとき、シフト・レジスタの内容が受信器バッファに転送されます。 そして、UDRnレジスタのI/Oアドレスを読み取ることで、受信器バッファを読み取ることができます。

下記のコーディング例では、受信完了(RXCn)フラグのポーリング処理によるUSART受信を行う、簡単な関数を示します。 8ビットよりも短いデータ長のフレームを使用する場合、UDRnレジスタから読み取ったデータの上位ビットはゼロにマスクされます。 USARTはこの関数を使用するよりも前に初期化しておく必要があります。

| アセンブリ言語の例(1) |

USART_Receive: ; 受信データを待つ sbis UCSRnA, RXCn rjmp USART_Receive ; 受信データをバッファから読み取ってリターン in r16, UDRn ret |

| C言語の例(1) |

unsigned char USART_Receive( void )

{

/* 受信データを待つ */

while ( !(UCSRnA & (1<<RXCn)) )

;

/* 受信データをバッファから読み取ってリターン */

return UDRn;

}

|

注: 1. 「サンプル・コードについて」(p.7)を参照

この関数は、RXCnフラグをチェックすることで受信バッファ内にデータが現れるのを待ち、バッファを読み取って値を返すという簡単なものです。

9ビット長のキャラクタを使用している(UCSZn=7)場合、第9ビットをUCSRnBレジスタのRXB8nビットから読み取ってから、その後でUDRnレジスタの低位ビットを読み取る必要があります。 この手順は、FEn、DORn、UPEn各ステータス・フラグについても同様です。 UCSRnAレジスタからステータスを読み取り、その後でUDRnレジスタを読み込んでください。 UDRnレジスタのI/Oアドレスを読み取ることにより、受信バッファFIFOのステータスが変化するので、それにともなってFIFOに格納されているTXB8n、FEn、DORn、UPEn各ビットが変化してしまいます。

下記のコーディング例では、第9ビットとステータス・フラグを扱ったUSART受信を行う簡単な関数を示します。

| アセンブリ言語の例(1) |

USART_Receive: ; データの受信を待つ sbis UCSRnA, RXCn rjmp USART_Receive ; ステータスと第9ビットを読み取り、その後バッファからデータを読み取る in r18, UCSRnA in r17, UCSRnB in r16, UDRn ; エラーの場合、-1を返す andi r18,(1<<FEn)|(1<<DORn)|(1<<UPEn) breq USART_ReceiveNoError ldi r17, HIGH(-1) ldi r16, LOW(-1) USART_ReceiveNoError: ; 第9ビットのみを取り出し、リターン lsr r17 andi r17, 0x01 ret |

| C言語の例(1) |

unsigned int USART_Receive( void )

{

unsigned char status, resh, resl;

/* データの受信を待つ */

while ( !(UCSRnA & (1<<RXCn)) )

;

/* ステータスと第9ビットを読み取り、その後バッファからデータを読み取る */

status = UCSRnA;

resh = UCSRnB;

resl = UDRn;

/* エラーの場合、-1を返す */

if ( status & (1<<FEn)|(1<<DORn)|(1<<UPEn) )

return -1;

/* 第9ビットのみを取り出し、リターン */

resh = (resh >> 1) & 0x01;

return ((resh << 8) | resl);

}

|

注: 1. 「サンプル・コードについて」(p.7)を参照

この受信関数の例では、全てのI/Oレジスタの値をレジスタ・ファイルに読み込んでから、演算処理を行っています。 これにより、受信バッファが開放されて、新しいデータを受け取る準備を早くできるため、受信バッファの使用率が最適化されます。

USART受信器には受信器の状態を表すフラグが一つあります。

受信完了(RXCn)フラグは受信バッファ内に未読のデータがあるかどうかを表しています。 まだ読み取っていないデータが受信バッファ内にある場合に1になり、受信バッファが空のとき(未読のデータが無い場合)このフラグは0になります。 受信器が無効(RXENn = 0)に設定された場合、受信バッファの内容は破棄されるため、RXCnフラグは0になります。

UCSRnBレジスタの受信完了割込み有効(RXCIEn)ビットがセットされている場合、RXCnフラグがセットされている間(グローバル割込みフラグが有効に なっている場合)USART受信完了割込みが発生します。 割込みを利用してデータ受信処理を行っている場合、受信完了割込みルーチン内でUDRnレジスタから受信データを読み取り、RXCnフラグをクリアしなければなりません。そうしないと、割込み処理ルーチンが終了すると同時に、新しい割込みが発生してしまうからです。

USART受信器には三つのエラー・フラグがあります。 フレーム・エラー(FEn)、データ・オーバーラン(DORn)、およびパリティ・エラー(UPEn)です。 これら全てのフラグは、UCSRnAレジスタの読み取りによりアクセスできます。 全てのエラー・フラグには、受信バッファ内に配置されており、各フレームごとのエラー・ステータスを表しているという共通点があります。 バッファでは各エラー・フラグを保存しているため、UCSRnAレジスタを受信バッファ(UDRnレジスタ)より先に読み出す必要があります。 これは、UDRnレジスタのI/Oアドレスの読み取りによってバッファの読み出し位置が変化してしまうためです。

また、全てのフラグについて同様に、各フラグのI/Oアドレスのビット位置にソフトウェアにより書き込みを行うことでは変更することはできません。 しかし、将来のUSART実装との互換性のため、UCSRnAレジスタに書き込みを行う場合、全てのフラグを0にセットしてください。 どのエラー・フラグにも割込みを発生させる機能はありません。

フレーム・エラー(FEn)フラグは、次に受信バッファから読み出すフレームについて、最初のストップ・ビットの状態を表しています。 ストップ・ビットを正しく(1として)読み取った場合にFEnフラグは0になり、ストップ・ビットが正しくない(0になっている)場合にFEnフラグが1になります。 このフラグを使って、同期の外れた状態の検出、ブレーク状態の検出、プロトコル処理を行うことができます。 受信器は最初のストップ・ビット以外は全て無視するため、FEnフラグはUCSRnCレジスタのUSBSnビットの設定とは無関係です。 将来のデバイスとの互換性のため、UCSRnAレジスタに書き込みを行う場合は、常にこのビットを0にしてください。

データ・オーバーラン(DORn)フラグは、受信バッファがいっぱいになってしまったことでデータが失われた状態を表します。 受信バッファがいっぱい(2キャラクタ)で、かつ受信シフト・レジスタ内に待機中のデータがある状態で、次のスタート・ビットが検出された場合に、データ・オーバーランが発生します。 DORnフラグがセットされている場合、最後にUDRnレジスタから読み出したフレームと、次にUDRnレジスタから読み出すフレームとの間で、一つ以上の通信フレームが失われています。 将来のデバイスとの互換性のため、UCSRnAレジスタに書き込みを行う場合は、常にこのビットを0にしてください。 受信したフレームがシフト・レジスタから受信バッファに正しく転送できた場合にDORnフラグがクリアされます。

パリティ・エラー(UPEn)フラグは、次に受信バッファから読み出すフレームには、受信時にパリティ・エラーがあったことを表しています。 パリティ・チェック機能を有効にしていない場合、UPEnビットは常に0になります。 将来のデバイスとの互換性のため、UCSRnAレジスタに書き込みを行う場合は、常にこのビットを0にしてください。 詳細については、「パリティ・ビットの算出」(p.175)と「パリティ・チェッカー」(p.183)を参照してください。

USARTパリティ・モード・ビットの上位(UPMn1)ビットをセットすると、パリティ・チェッカーが有効になります。 パリティ・チェックの種別(奇数/偶数)は、UPMn0ビットで選択します。 パリティ・チェッカーが有効になっている場合、受信したフレームのデータ・ビットから算出したパリティと通信フレーム内のパリティ・ビットを比較します。 比較結果は受信バッファ内に受信データ、ストップ・ビットとともに格納されます。 パリティ・エラー(UPEn)フラグをソフトウェアで読み取り、そのフレームにパリティ・エラーが生じているかどうか確認することができます。

受信バッファから読み出す次のキャラクターに受信時にパリティ・エラーがあり、その時点でパリティ・チェック機脳が有効になっている(UPMn1 = 1)場合、UPEnビットがセットされます。 このビットの内容は、受信バッファ(UDRnレジスタ)を読み出すまで有効です。

送信器と異なり、受信器の無効化は即座に実行されます。 したがって、通信中の受信データがある場合、そのデータは失われます。 受信器を無効にする(RXENnに0をセットする)と、RxCn端子の機能優先はなくなり通常のポート端子に戻ります。 受信器を無効した時点で、受信バッファのFIFOの内容は破棄されます。 バッファ内に残っているデータは失われます。

受信バッファのFIFOは受信器を無効にすると、その内容が破棄され、データの存在しない状態となります。 未読のデータは失われます。 エラー状態など、通常の動作においてバッファの内容を破棄する必要がある場合、RXCnフラグがクリアされるまでUDRnレジスタのI/Oアドレスを読み出してください。 下記のコーディング例は、受信バッファの内容を破棄する方法について示したものです。

| アセンブリ言語の例(1) |

USART_Flush: sbis UCSRnA, RXCn ret in r16, UDRn rjmp USART_Flush |

| C言語の例(1) |

void USART_Flush( void )

{

unsigned char dummy;

while ( UCSRnA & (1<<RXCn) ) dummy = UDRn;

}

|

注: 1. 「サンプル・コードについて」(p.7)を参照

USARTには、非同期データの受信を行うためにクロック・リカバリ・ユニット、およびデータ・リカバリ・ユニットが組み込まれています。 クロック・リカバリ回路はチップ内部で生成されるボーレート・クロックと、RxDn端子で受信する非同期シリアル通信フレームとの同期を取るために使用されています。 データ・リカバリ回路は各受信ビットについてサンプリングとロー・パス・フィルター処理を行い、受信器のノイズに対する耐性を向上させます。 非同期通信受信の正常動作範囲は、内蔵のボーレート・クロックの精度、受信フレームの通信速度、通信フレームのビット数によって変わります。

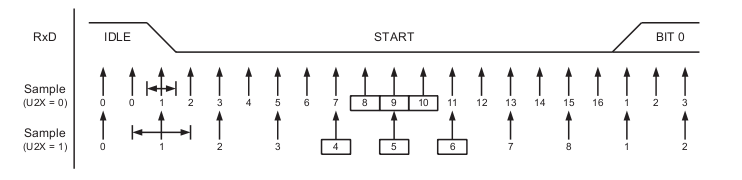

クロック・リカバリ回路は内部クロックを受信シリアル通信フレームと同期させます。 Figure 19-5は、受信フレームのスタート・ビットをサンプリングする手順について示したものです。 サンプリング・レートは、通常モードではボーレートの16倍、倍速モードでは8倍になっています。 水平方向の矢印はサンプリング処理によって同期タイミングに変動が生じることを表しています。 倍速モード(U2Xn = 1)を使用すると、タイミングの変動する範囲が大きいことが分かります。 「0」とかかれたサンプリング(Sample 0)は、RxDn信号が待機状態(通信が行われていない状態)でのサンプリングを表しています。

クロック・リカバリ回路がRxDn信号のHigh(待機状態)からLow(スタート)への変化を検出すると、スタート・ビットの検出シーケンスが始まります。 図中のサンプリング「1」(Sample 1)を、最初の0状態のサンプリングと考えてみましょう。 その後、クロック・リカバリ回路は、通常モードでは「8」、「9」、「10」を、倍速モードでは「4」、「5」、「6」を利用して(図中に四角で囲まれた番号)、有効なスタート・ビットが受信されたかどうかを判断します。 この三つのサンプリングにおいて、二つ、ないし三つがHighレベルであった場合(多数決出力)、そのスタート・ビットはスパイク・ノイズとして破棄され、受信器は次のHighからLowへの信号変化の探索を再開します。 有効なスタート・ビットを検出した場合、クロック・リカバリ回路は同期した状態となり、データ・リカバリ処理が開始されます。 この同期手順は、スタート・ビットごとに毎回繰り返されます。

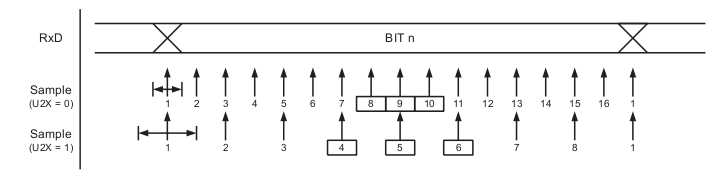

受信器のクロックがスタート・ビットと同期すると、データ・リカバリ処理を開始できる状態になります。 データ・リカバリ・ユニットは、各ビットごとに、通常モードで16個、倍速モードで8個の状態を持つステート・マシンを利用します。 Figure 19-6は、データ・ビットとパリティ・ビットのサンプリングの様子を表したものです。 それぞれのサンプリングには、リカバリ・ユニットの各ステートに相当する番号がつけてあります。

受信したビットの論理値は、受信ビットの中央部分の三つのサンプリング結果の多数決をとることにより決定されます。 この中央部のサンプリングとは、四角で囲まれた番号により強調表示されているものです。 多数決による決定の手順は、二つ、ないし三つ全てのサンプリング結果がHighレベルの場合、受信ビットは論理値1として記録されるというものです。

二つ、ないし三つのサンプリング結果がLowレベルの場合、受信ビットは論理値0として記録されます。 この多数決による処理はRxDn端子の受信信号に対するロー・パス・フィルターとして機能します。 ビットのリカバリの手順は、最初のストップ・ビットを含め、1フレームの受信が完了するまで繰り返されます。

なお、受信器ではフレーム内の最初のストップ・ビットのみ使用します。

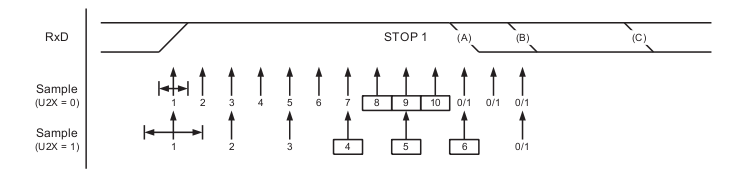

Figure 19-7は、ストップ・ビットのサンプリングと、その後に次フレームのスタート・ビットが最も早く始まる場合を表したものです。

ストップ・ビットでの多数決処理は、通信フレーム内の他のビットと同様に行われます。 ストップ・ビットが論理値0として記録された場合、フレーム・エラー(FEn)フラグがセットされます。

次のフレームのスタート・ビットを意味するストップ・ビット後のHighからLowへの変化は、多数決処理を行った最後のサンプリングの直後に現れる可能性があります。 通常モードでは、最初のLowレベルのサンプリングは、Figure 19-7中の(A)で示された位置にくる可能性があります。 倍速モードでは、最初のLowレベルのサンプリングは、(B)より後でなければなりません。 (C)の位置はストップビットの最大長を表しています。 スタート・ビットの検出をどこまで早くできるかは、受信器の正常動作範囲に影響します。

受信器の正常動作範囲は、受信信号のビット・レートと内部で生成されたボーレートとの差異に影響を受けます。 送信器の送信が速すぎるビット・レート、または遅すぎるビット・レートの場合、あるいは、受信器の内蔵ボーレートが基本周波数に近い値(Table 19-2を参照)ではない場合、受信器は通信フレームをスタート・ビットにより同期させることができなくなります。

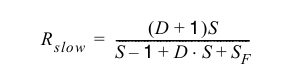

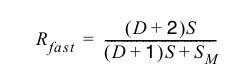

次の式により、受信データのビット・レートと内蔵受信器のボーレートとの比を計算できます。

| D | キャラクターのビット長とパリティ・ビット長の合計 (D = 5から10ビット) |

|---|---|

| S | ビットごとのサンプリング数。通常モードではS = 16、倍速モードではS = 8 |

| S_F | 多数決処理に使用される最初のサンプリング番号。通常モードではS_F = 8、倍速モードではS_F = 4 |

| S_M | 多数決処理に使用される中央のサンプリング番号。通常モードではS_F = 9、倍速モードではS_F = 5 |

| R_slow | その受信器のボーレートにおける、受信可能なデータの最も遅いビット・レート。 |

| R_fast | その受信器のボーレートにおける、受信可能なデータの最も速いビット・レート。 |

Table 19-2とTable 19-3は、受信器のボーレート誤差の許容範囲をリストにしたものです。 通常モードの方が、ボーレートの変動に対して大きな許容範囲を持っていることが分かります。

|

D (データ+パリティ) |

R_slow (%) | R_fast (%) | 最大合計誤差 (%) | 受信器の推奨最大誤差 (%) |

|---|---|---|---|---|

| 5 | 93.20 | 106.67 | +6.67/-6.8 | ± 3.0 |

| 6 | 94.12 | 105.79 | +5.79/-5.88 | ± 2.5 |

| 7 | 94.81 | 105.11 | +5.11/-5.19 | ± 2.0 |

| 8 | 95.36 | 104.58 | +4.58/-4.54 | ± 2.0 |

| 9 | 95.81 | 104.14 | +4.14/-4.19 | ± 1.5 |

| 10 | 96.17 | 103.78 | +3.78/-3.83 | ± 1.5 |

|

D (データ+パリティ) |

R_slow (%) | R_fast (%) | 最大合計誤差 (%) | 受信器の推奨最大誤差 (%) |

|---|---|---|---|---|

| 5 | 94.12 | 105.66 | +5.66/-5.88 | ± 2.5 |

| 6 | 94.92 | 104.92 | +4.92/-5.08 | ± 2.0 |

| 7 | 95.52 | 104.35 | +4.35/-4.48 | ± 1.5 |

| 8 | 96.00 | 103.90 | +3.90/-4.00 | ± 1.5 |

| 9 | 96.39 | 103.53 | +3.53/-3.61 | ± 1.5 |

| 10 | 96.70 | 103.23 | +3.23/-3.30 | ± 1.0 |

「受信器の推奨最大誤差」は、受信器側と送信器側の両方に同じ最大誤差があるという仮定のもので算出したものです。

受信器のボーレート誤差には、二つの要因により生じる可能性があります。 一つは、受信器のシステム・クロック(XTAL)には、供給電源電圧と動作温度の変化による小さな変動が必ず存在するということです。 クリスタル発振子をシステム・クロックとして利用している場合には問題になることはほとんどありませんが、セラミック発振子の場合、システム・クロックは発振子の許容誤差に応じた2%以上の変動が生じる場合があります。 もう一つの誤差の要因は、もう少し抑制が簡単なものです。 ボーレート・ジェネレータは、必ずしもシステム・クロックの周波数を正確に分周して必要なボーレートを得ることができるとは限りません。 この場合、可能であれば、許容可能な低い誤差になるようにUBRRnレジスタの値を使用することで解決できます。

UCSRnAレジスタのマルチ・プロセッサ通信モード(MPCMn)ビットをセットすると、USART受信器で受信した通信フレームのフィルター機能が有効になります。 アドレス情報を含んでいないフレームは無視され、受信バッファに入力されません。 この機能によって、複数のMCUが同一のシリアル・バス上で通信をしているシステムにおいて、CPUによって処理しなければならない受信フレーム数を効果的に減らします。 送信器の動作はMPCMnビットの設定に影響を受けませんが、マルチ・プロセッサ通信モードを利用しているシステムを構成している場合は異なった使い方をする必要があります。

受信器が5から8データ・ビットのフレームを受信するように設定されている場合、最初のストップ・ビットは、そのフレームに含まれているのがデータ情報かアドレス情報かを示します。 受信器が第9ビットのあるフレームを使用するように設定されている場合、第9ビット(RXB8n)がアドレス・フレームとデータ・フレームの識別に使用されます。 フレームの種別を表すビット(最初のストップ・ビット、あるいは第9ビット)が1の場合、そのフレームはアドレス情報を含んでいます。 フレームの種別を表すビット(最初のストップ・ビット、あるいは第9ビット)が0の場合は、データ・フレームです。

マルチ・プロセッサ通信モードの利用によって、複数のスレーブMCUがマスターCPUからのデータを受信することができるようになります。 これは、まずアドレス・フレームを解析して、どのMCUがしていされたかを判断することにより可能です。 スレーブMCUが指定されると、指定されたMCUは次のフレームを通常どおりデータ・フレームとして受信し、他のスレーブMCUは新たなアドレス・フレームを受信するまで受信フレームを無視します。

マスターとして動作するMCUでは、9ビット・キャラクターのフレーム・フォーマット(UCSZn = 7)を使用できます。 第9ビット(TXB8n)は、アドレス・フレームではセット(TXB8n = 1)し、データ・フレームではクリア(TXB8n = 0)して、送信を行います。 この場合、スレーブMCUは9ビット・キャラクターのフレーム・フォーマットを使用するように設定する必要があります。

下記の手順により、マルチ・プロセッサ通信モードでデータ交換を行います。

5から8ビットのキャラクターのフレーム・フォーマットのどれでも使用することができますが、受信器がnビットとn+1ビットのフレーム・フォーマットの使用を切り換えなければならないため実用的ではありません。 この場合、送受信器が同じキャラクター・サイズの設定を使用するために、全二重通信が困難になります。 5から8ビットのキャラクターのフレーム・フォーマットを使用する場合は、送信器は2つのストップ・ビットを使用する設定(USBSn = 1)にして、最初のストップ・ビットをフレーム種別の識別に使用する必要があります。

MPCMnビットのセットやクリアに、リード・モディファイ・ライトの命令(SBIとCBI)を使用しないでください。 MPCMnビットはTXCnフラグと同じI/Oアドレスを共有しているので、SBIやCBI命令を使うと意図していないTXCnフラグのクリアを行う可能性があります。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| RXB[7:0] | UDRn (リード) | ||||||||

| TXB[7:0] | UDRn (ライト) | ||||||||

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

USART送信データ・バッファ・レジスタとUSART受信データ・バッファ・レジスタは同一のI/Oアドレスを共有しており、ともにUSARTデータ・レジスタ、UDRnと呼びます。 送信データバッファ・レジスタ(TXB)は、UDRnレジスタのアドレスにデータ書き込みをした場合の転送先となります。 UDRnレジスタのアドレスを読み取ると、受信データバッファ・レジスタ(RXB)の値が返ってきます。

5、6、7ビットのキャラクターでは、上位の未使用ビットは送信器側では無視され、受信器では0がセットされます。

送信バッファへの書き込みは、UCSRnAレジスタのUDREnフラグがセットされている場合にのみ可能です。

UDREnフラグがセットされていないときにUDRnレジスタに書き込んだデータはUSART送信器に無視されます。 送信バッファにデータを書き込んだとき、送信器が有効になっていれば、送信器は送信用シフト・レジスタが空の場合、そのデータをシフト・レジスタに転送します。 そして、データはTxDn端子からシリアル・データとなって送信されます。

受信バッファには、2レベルのFIFOがあります。 FIFOの状態は受信バッファにアクセスがあった場合に変化します。 この受信バッファの設計上の理由により、リード・モディファイ・ライト命令(SBIとCBI)をこのアドレスに対して使用しないでください。 ビット・テスト命令(SBICとSBIS)についても、FIFOの状態を変化させるため、使用は慎重に行う必要があります。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| RXCn | TXCn | UDREn | FEn | DORn | UPEn | U2Xn | MPCMn | UCSRnA | |

| Read/Write | R | R/W | R | R | R | R | R/W | R/W | |

| 初期値 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 |

このフラグは、受信バッファ内に読み出していないデータがある場合にセットされ、受信バッファが空になったとき(読み出していないデータが無い)にクリアされます。 受信器が無効になると、受信バッファの内容が破棄されるためRXCnフラグは0になります。 RXCnフラグを用いて、受信完了割込みを発生させることができます(RXCIEnビットの説明を参照)。

このフラグは、送信用シフト・レジスタ内の通信フレームが完全に送出され、送信バッファ(UDRn)に新しいデータが存在しないときにセットされます。 送信完了割込みが実行されると、TXCnフラグは自動的にクリアされます。このビットに1を書き込んでクリアすることもできます。 TXCnフラグを用いて送信完了割込みを発生させることができます(TXCIEnビットの説明を参照)。

UDREnフラグは、送信バッファ(UDRnレジスタ)に新しいデータを書き込む準備ができていることを表しています。 UDREnが1の場合送信バッファは空であり、書き込みを行うことができます。 UDREnフラグを用いてデータ・レジスタ・エンプティ割込みを発生させることができます(UDRIEnビットの説明を参照)。

UDREnフラグはリセット直後はセットされ、送信準備ができていることを表しています。

このビットは、受信バッファにある次のデータの受信時にフレーム・エラーが発生している場合にセットされます。 つまり、受信バッファ内の次のキャラクタの最初のストップ・ビットが0である場合です。 このビットは、受信バッファ(UDRn)レジスタを読み出すまで有効です。 受信データのストップ・ビットが1の場合、FEnビットは0になります。

UCSRnAレジスタに書き込みを行う場合、このビットは必ず0にしてください。

このビットは、データ・オーバーランの状態が検出された場合にセットされます。 受信器のバッファがいっぱいの状態(2キャラクタ)で、受信用シフト・レジスタに待機中のデータがあり、新しいキャラクタのスタート・ビットを検出した場合に、データ・オーバーランが発生します。 このビットは、受信バッファ(UDRnレジスタ)を読み取る時点まで有効です。 UCSRnAレジスタに書き込みを行う場合、このビットは必ず0にしてください。

このビットは、パリティ・チェック機能が有効(UPMn1 = 1)のとき、次に受信バッファから読み取るキャラクタの受信時にパリティー・エラーが発生している場合にセットされます。 このビットは、受信バッファ(UDRnレジスタ)を読み取る時点まで有効です。 UCSRnAレジスタに書き込みを行う場合、このビットは必ず0にしてください。

このビットは、非同期通信モードでのみ有効です。 同期通信モードでは、このビットに0を書き込んでください。

このビットに1を書き込むと、ボーレート分周器の分周比を16から8に減らすことにより、非同期通信での転送レートを2倍にします。

このビットによって、マルチ・プロセッサ通信モードを有効にします。 MPCMnビットに1を書き込むと、USART受信器で受信するフレームのうち、アドレス情報を含んでいないものを全て無視します。 MPCMnビットの設定による送信器の動作への影響はありません。 詳細については、「マルチ・プロセッサ通信モード」(p.187)を参照してください。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| RXCIEn | TXCIEn | UDRIEn | RXENn | TXENn | UCSZn2 | RXB8n | TXB8n | UCSRnB | |

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

このビットに1を書き込むと、RXCnフラグによる割込みが発生します。 RXCIEnビットに1がセットされていて、かつ、SREGのグローバル割込みフラグに1がセットされている場合に、UCSRnAレジスタのRXCnビットがセットされると、USART受信完了割込みが発生します。

このビットに1を書き込むと、TXCnフラグによる割込みが発生します。 TXCIEnビットに1がセットされていて、かつ、SREGのグローバル割込みフラグに1がセットされている場合に、UCSRnAレジスタのTXCnビットがセットされると、USART送信完了割込みが発生します。

このビットに1を書き込むと、UDREnフラグによる割込みが発生します。 UDRIEnビットに1がセットされていて、かつ、SREGのグローバル割込みフラグに1がセットされている場合に、UCSRnAレジスタのUDREnビットがセットされると、データ・レジスタ・エンプティ割込みが発生します。

このビットに1を書き込むとUSART受信器が有効になります。 受信器が有効になると、RxDn端子では通常のポート機能よりもUSART受信器の機能が優先されます。 受信器を無効にすると受信バッファの内容が破棄され、FEn、DORn、UPEn各フラグの内容も無効になります。

このビットに1を書き込むとUSART送信器が有効になります。 送信器が有効になると、TxDn端子では通常のポート機能よりもUSART送信器の機能が優先されます。 送信器を無効に設定(TXEnに0を書き込み)しても、処理中、および待機中の送信が完了するまで、つまり、送信用シフト・レジスタと送信バッファ・レジスタに送信データが全くない状態になるまで、送信器は無効化されません。 送信器が無効になると、TxDn端子は機能優先が解除されて通常のポート端子になります。

UCSZn2ビットとUCSRnCレジスタのUCSZn1:0ビットの組み合わせにより、受信器と送信器で扱う通信フレームのデータ・ビット数(キャラクター・サイズ)を設定します。

RXB8nは、9ビット長データの通信フレームで動作させる場合の、受信データ・ビットの第9ビットです。 UDRnレジスタにある下位ビットを読み取る前に、このビットを読み取る必要があります。

TXB8nは、9ビット長データの通信フレームで動作させる場合の、送信データ・ビットの第9ビットです。 UDRnレジスタに下位ビットを書き込む前に、このビットを書き込む必要があります。

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| UMSELn1 | UMSELn0 | UPMn1 | UPMn0 | USBSn | UCSZn1 | UCSZn0 | UCPOLn | UCSRnC | |

| Read/Write | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | |

| 初期値 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

Table 19-4にあるとおり、このビットでUSARTnの動作モードを選択します。

| UMSELn1 | UMSELn0 | モード |

|---|---|---|

| 0 | 0 | 非同期USARTモード |

| 0 | 1 | 同期USARTモード |

| 1 | 0 | (予約) |

| 1 | 1 | マスターSPIモード(MSPIM)(1) |

注意: 1.マスターSPIモード(MSPIM)については、「USARTのSPIモード」(p.198)に説明があります。

このビットでパリティ・ビットの生成とチェック機能の種別を設定します。 パリティを有効にすると、送信器では自動的に各送信フレームのデータ・ビットのパリティを計算して送信します。 受信器では、受信データのパリティを計算し、UPMnビットで設定したパリティと比較します。

パリティの相違を検出すると、UCSRnAレジスタのUPEnフラグがセットされます。

| UPMn1 | UPMn0 | パリティ・ビットのモード |

|---|---|---|

| 0 | 0 | パリティ無効 |

| 0 | 1 | (予約) |

| 1 | 0 | パリティ有効、偶数パリティ |

| 1 | 1 | パリティ有効、奇数パリティ |

このビットで送信器によって挿入されるストップ・ビットの数を選択します。 受信器では、この設定は無視されます。

| USBSn | ストップ・ビットの数 |

|---|---|

| 0 | 1ビット |

| 1 | 2ビット |

UCSZn1:0ビットとUCSRnBレジスタのUCSZn2ビットの組み合わせにより、受信器と送信器で扱う通信フレームのデータ・ビット数(キャラクター・サイズ)を設定します。

| UCSZn2 | UCSZn1 | UCSZn0 | キャラクター・サイズ |

|---|---|---|---|

| 0 | 0 | 0 | 5ビット |

| 0 | 0 | 1 | 6ビット |

| 0 | 1 | 0 | 7ビット |

| 0 | 1 | 1 | 8ビット |

| 1 | 0 | 0 | (予約) |

| 1 | 0 | 1 | (予約) |

| 1 | 1 | 0 | (予約) |

| 1 | 1 | 1 | 9ビット |

このビットは同期通信モードでのみ使用します。 非同期通信モードでは、このビットに0を書き込んでください。 UPOLnビットによって、出力データの変化タイミングや入力データのサンプリング・タイミングと、同期クロック(XCKn信号)の関係を設定します。

| UCPOLn | 送信データの変化(TxDn端子への出力) | 受信データのサンプリング(RxDn端子からの入力) |

|---|---|---|

| 0 | XCKnの立ち上がりエッジ | XCKnの立ち下がりエッジ |

| 1 | XCKnの立ち下がりエッジ | XCKnの立ち上がりエッジ |

| ビット | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| - | - | - | - | UBRRn[11:8] | UBRRnH | ||||

| UBRRn[7:0] | UBRRnL | ||||||||

| Read/Write | R | R | R | R | R/W | R/W | R/W | R/W | |

| R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W | ||

| 初期値 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ||

これらのビットは将来の使用のため予約となっています。 将来のデバイスとの互換性のため、UBRRnHレジスタに書き込みを行う際は、必ずこれらのビットに0を書き込んでください。

このレジスタは、USARTのボーレートを設定する12ビットのレジスタです。 UBRRnHレジスタに上位4ビット、UBRRnLレジスタに下位8ビットのボーレート設定値が含まれます。 ボーレートを変更すると送受信器で処理中の通信データは異常な値となります。 UBRRnLレジスタへの書き込みを行うと、ボーレート分周器への変更は即座に反映されます。

標準的なクリスタル発振子やセラミック発振子の周波数に対して、Table 19-9にあるUBRRnレジスタの設定値を使用することで、最も一般的に使われている非同期通信のボーレートを生成することができます。 実際に生成されるボーレートが、目的のボーレート値に対して0.5%よりも小さい誤差となるUBRRnレジスタの値は表中で太字になっています。 大きな誤差をもつボーレートを使用することもできますが、その場合、受信器はノイズに対する耐性が低くなり、特に長いビット長の通信フレームを使用する場合に悪化します(「非同期通信の正常動作範囲 」(p.186)を参照)。 誤差は次の式により計算されています。

![Error[%] = (\frac{BaudRate_ClosestMatch}{BaudRate} - 1) * 100%](equation-chapter19-baudrate-error.png)

| ボーレート(bps) | f_osc = 1.0000MHz | f_osc = 1.8432MHz | f_osc = 2.0000MHz | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| U2Xn = 0 | U2Xn = 1 | U2Xn = 0 | U2Xn = 1 | U2Xn = 0 | U2Xn = 1 | |||||||

| UBRRn | 誤差 | UBRRn | 誤差 | UBRRn | 誤差 | UBRRn | 誤差 | UBRRn | 誤差 | UBRRn | 誤差 | |

| 2400 | 25 | 0.2% | 51 | 0.2% | 47 | 0.0% | 95 | 0.0% | 51 | 0.2% | 103 | 0.2% |

| 4800 | 12 | 0.2% | 25 | 0.2% | 23 | 0.0% | 47 | 0.0% | 25 | 0.2% | 51 | 0.2% |

| 9600 | 6 | -7.0% | 12 | 0.2% | 11 | 0.0% | 23 | 0.0% | 12 | 0.2% | 25 | 0.2% |

| 14.4k | 3 | 8.5% | 8 | -3.5% | 7 | 0.0% | 15 | 0.0% | 8 | -3.5% | 16 | 2.1% |

| 19.2k | 2 | 8.5% | 6 | -7.0% | 5 | 0.0% | 11 | 0.0% | 6 | -7.0% | 12 | 0.2% |

| 28.8k | 1 | 8.5% | 3 | 8.5% | 3 | 0.0% | 7 | 0.0% | 3 | 8.5% | 8 | -3.5% |

| 38.4k | 1 | -18.6% | 2 | 8.5% | 2 | 0.0% | 5 | 0.0% | 2 | 8.5% | 6 | -7.0% |

| 57.6k | 0 | 8.5% | 1 | 8.5% | 1 | 0.0% | 3 | 0.0% | 1 | 8.5% | 3 | 8.5% |

| 76.8k | – | – | 1 | -18.6% | 1 | -25.0% | 2 | 0.0% | 1 | -18.6% | 2 | 8.5% |

| 115.2k | – | – | 0 | 8.5% | 0 | 0.0% | 1 | 0.0% | 0 | 8.5% | 1 | 8.5% |

| 230.4k | – | – | – | – | – | – | 0 | 0.0% | – | – | – | – |

| 250k | – | – | – | – | – | – | – | – | – | – | 0 | 0.0% |

| 最大(1) | 62.5 kbps | 125 kbps | 115.2 kbps | 230.4 kbps | 125 kbps | 250 kbps | ||||||

| ボーレート(bps) | f_osc = 3.6864MHz | f_osc = 4.0000MHz | f_osc = 7.3728MHz | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| U2Xn = 0 | U2Xn = 1 | U2Xn = 0 | U2Xn = 1 | U2Xn = 0 | U2Xn = 1 | |||||||

| UBRRn | 誤差 | UBRRn | 誤差 | UBRRn | 誤差 | UBRRn | 誤差 | UBRRn | 誤差 | UBRRn | 誤差 | |

| 2400 | 95 | 0.0% | 191 | 0.0% | 103 | 0.2% | 207 | 0.2% | 191 | 0.0% | 383 | 0.0% |

| 4800 | 47 | 0.0% | 95 | 0.0% | 51 | 0.2% | 103 | 0.2% | 95 | 0.0% | 191 | 0.0% |

| 9600 | 23 | 0.0% | 47 | 0.0% | 25 | 0.2% | 51 | 0.2% | 47 | 0.0% | 95 | 0.0% |

| 14.4k | 15 | 0.0% | 31 | 0.0% | 16 | 2.1% | 34 | -0.8% | 31 | 0.0% | 63 | 0.0% |

| 19.2k | 11 | 0.0% | 23 | 0.0% | 12 | 0.2% | 25 | 0.2% | 23 | 0.0% | 47 | 0.0% |

| 28.8k | 7 | 0.0% | 15 | 0.0% | 8 | -3.5% | 16 | 2.1% | 15 | 0.0% | 31 | 0.0% |

| 38.4k | 5 | 0.0% | 11 | 0.0% | 6 | -7.0% | 12 | 0.2% | 11 | 0.0% | 23 | 0.0% |

| 57.6k | 3 | 0.0% | 7 | 0.0% | 3 | 8.5% | 8 | -3.5% | 7 | 0.0% | 15 | 0.0% |

| 76.8k | 2 | 0.0% | 5 | 0.0% | 2 | 8.5% | 6 | -7.0% | 5 | 0.0% | 11 | 0.0% |

| 115.2k | 1 | 0.0% | 3 | 0.0% | 1 | 8.5% | 3 | 8.5% | 3 | 0.0% | 7 | 0.0% |

| 230.4k | 0 | 0.0% | 1 | 0.0% | 0 | 8.5% | 1 | 8.5% | 1 | 0.0% | 3 | 0.0% |

| 250k | 0 | -7.8% | 1 | -7.8% | 0 | 0.0% | 1 | 0.0% | 1 | -7.8% | 3 | -7.8% |

| 0.5M | – | – | 0 | -7.8% | – | – | 0 | 0.0% | 0 | -7.8% | 1 | -7.8% |

| 1M | – | – | – | – | – | – | – | – | – | – | 0 | -7.8% |

| 最大(1) | 230.4 kbps | 460.8 kbps | 250 kbps | 0.5 Mbps | 460.8 kbps | 921.6 kbps | ||||||

| ボーレート(bps) | f_osc = 8.0000MHz | f_osc = 11.0592MHz | f_osc = 14.7456MHz | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| U2Xn = 0 | U2Xn = 1 | U2Xn = 0 | U2Xn = 1 | U2Xn = 0 | U2Xn = 1 | |||||||

| UBRRn | 誤差 | UBRRn | 誤差 | UBRRn | 誤差 | UBRRn | 誤差 | UBRRn | 誤差 | UBRRn | 誤差 | |

| 2400 | 207 | 0.2% | 416 | -0.1% | 287 | 0.0% | 575 | 0.0% | 383 | 0.0% | 767 | 0.0% |

| 4800 | 103 | 0.2% | 207 | 0.2% | 143 | 0.0% | 287 | 0.0% | 191 | 0.0% | 383 | 0.0% |

| 9600 | 51 | 0.2% | 103 | 0.2% | 71 | 0.0% | 143 | 0.0% | 95 | 0.0% | 191 | 0.0% |

| 14.4k | 34 | -0.8% | 68 | 0.6% | 47 | 0.0% | 95 | 0.0% | 63 | 0.0% | 127 | 0.0% |

| 19.2k | 25 | 0.2% | 51 | 0.2% | 35 | 0.0% | 71 | 0.0% | 47 | 0.0% | 95 | 0.0% |

| 28.8k | 16 | 2.1% | 34 | -0.8% | 23 | 0.0% | 47 | 0.0% | 31 | 0.0% | 63 | 0.0% |

| 38.4k | 12 | 0.2% | 25 | 0.2% | 17 | 0.0% | 35 | 0.0% | 23 | 0.0% | 47 | 0.0% |

| 57.6k | 8 | -3.5% | 16 | 2.1% | 11 | 0.0% | 23 | 0.0% | 15 | 0.0% | 31 | 0.0% |

| 76.8k | 6 | -7.0% | 12 | 0.2% | 8 | 0.0% | 17 | 0.0% | 11 | 0.0% | 23 | 0.0% |

| 115.2k | 3 | 8.5% | 8 | -3.5% | 5 | 0.0% | 11 | 0.0% | 7 | 0.0% | 15 | 0.0% |

| 230.4k | 1 | 8.5% | 3 | 8.5% | 2 | 0.0% | 5 | 0.0% | 3 | 0.0% | 7 | 0.0% |

| 250k | 1 | 0.0% | 3 | 0.0% | 2 | -7.8% | 5 | -7.8% | 3 | -7.8% | 6 | 5.3% |

| 0.5M | 0 | 0.0% | 1 | 0.0% | – | – | 2 | -7.8% | 1 | -7.8% | 3 | -7.8% |

| 1M | – | – | 0 | 0.0% | – | – | – | – | 0 | -7.8% | 1 | -7.8% |

| 最大(1) | 0.5 Mbps | 1 Mbps | 691.2 kbps | 1.3824 Mbps | 921.6 kbps | 1.8432 Mbps | ||||||

| ボーレート(bps) | f_osc = 16.0000MHz | f_osc = 18.4320MHz | f_osc = 20.0000MHz | |||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| U2Xn = 0 | U2Xn = 1 | U2Xn = 0 | U2Xn = 1 | U2Xn = 0 | U2Xn = 1 | |||||||

| UBRRn | 誤差 | UBRRn | 誤差 | UBRRn | 誤差 | UBRRn | 誤差 | UBRRn | 誤差 | UBRRn | 誤差 | |

| 2400 | 416 | -0.1% | 832 | 0.0% | 479 | 0.0% | 959 | 0.0% | 520 | 0.0% | 1041 | 0.0% |

| 4800 | 207 | 0.2% | 416 | -0.1% | 239 | 0.0% | 479 | 0.0% | 259 | 0.2% | 520 | 0.0% |

| 9600 | 103 | 0.2% | 207 | 0.2% | 119 | 0.0% | 239 | 0.0% | 129 | 0.2% | 259 | 0.2% |

| 14.4k | 68 | 0.6% | 138 | -0.1% | 79 | 0.0% | 159 | 0.0% | 86 | -0.2% | 173 | -0.2% |

| 19.2k | 51 | 0.2% | 103 | 0.2% | 59 | 0.0% | 119 | 0.0% | 64 | 0.2% | 129 | 0.2% |

| 28.8k | 34 | -0.8% | 68 | 0.6% | 39 | 0.0% | 79 | 0.0% | 42 | 0.9% | 86 | -0.2% |

| 38.4k | 25 | 0.2% | 51 | 0.2% | 29 | 0.0% | 59 | 0.0% | 32 | -1.4% | 64 | 0.2% |

| 57.6k | 16 | 2.1% | 34 | -0.8% | 19 | 0.0% | 39 | 0.0% | 21 | -1.4% | 42 | 0.9% |

| 76.8k | 12 | 0.2% | 25 | 0.2% | 14 | 0.0% | 29 | 0.0% | 15 | 1.7% | 32 | -1.4% |

| 115.2k | 8 | -3.5% | 16 | 2.1% | 9 | 0.0% | 19 | 0.0% | 10 | -1.4% | 21 | -1.4% |

| 230.4k | 3 | 8.5% | 8 | -3.5% | 4 | 0.0% | 9 | 0.0% | 4 | 8.5% | 10 | -1.4% |

| 250k | 3 | 0.0% | 7 | 0.0% | 4 | -7.8% | 8 | 2.4% | 4 | 0.0% | 9 | 0.0% |

| 0.5M | 1 | 0.0% | 3 | 0.0% | – | – | 4 | -7.8% | – | – | 4 | 0.0% |

| 1M | 0 | 0.0% | 1 | 0.0% | – | – | – | – | – | – | – | – |

| 最大(1) | 1 Mbps | 2 Mbps | 1.152 Mbps | 2.304 Mbps | 1.25 Mbps | 2.5 Mbps | ||||||